Questões de Concurso

Sobre amplificadores em engenharia eletrônica em engenharia eletrônica

Foram encontradas 141 questões

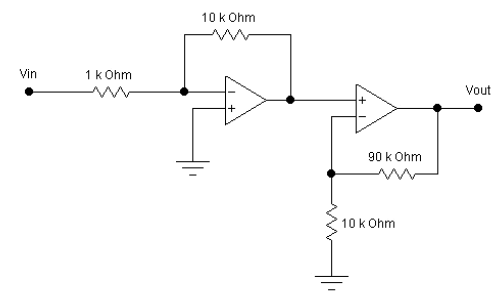

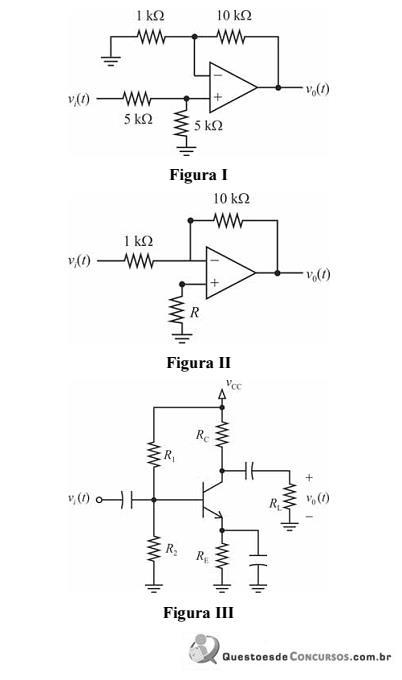

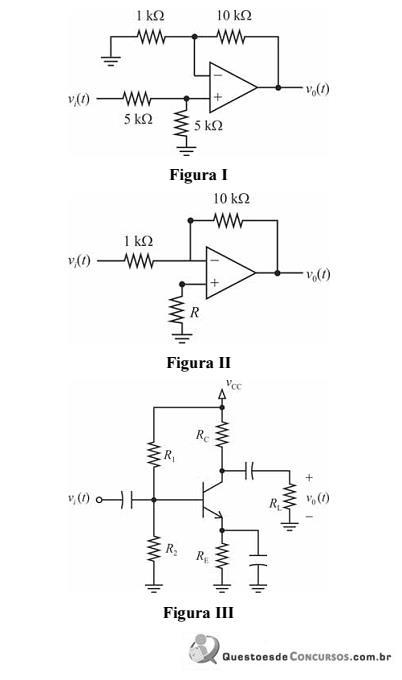

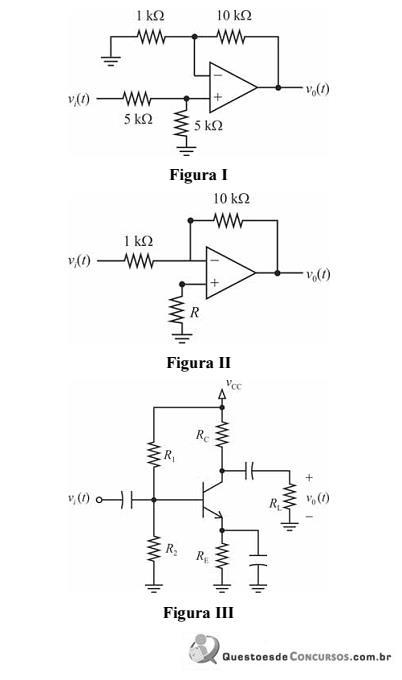

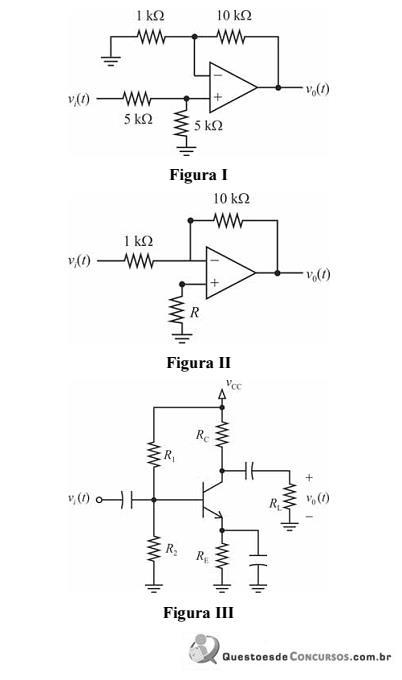

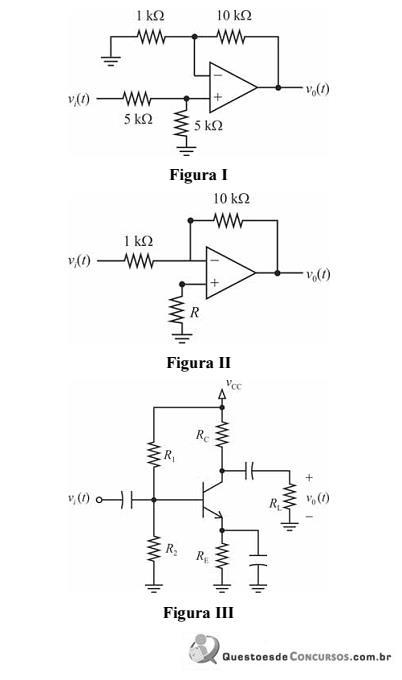

Julgue o item seguinte, referente aos amplificadores mostrados nas figuras I, II e III.

O circuito da figura II é um amplificador na configuração base

comum, e o seu ganho de corrente é menor que 2.

Qual é o valor r.m.s. desse sinal aleatório?

Se três estágios de amplificadores idênticos com ganho de tensão de 2 dB forem ligados em cascata, qual será o ganho total, em dB, e qual o efeito que ocorre na largura de faixa resultante dessa ligação?

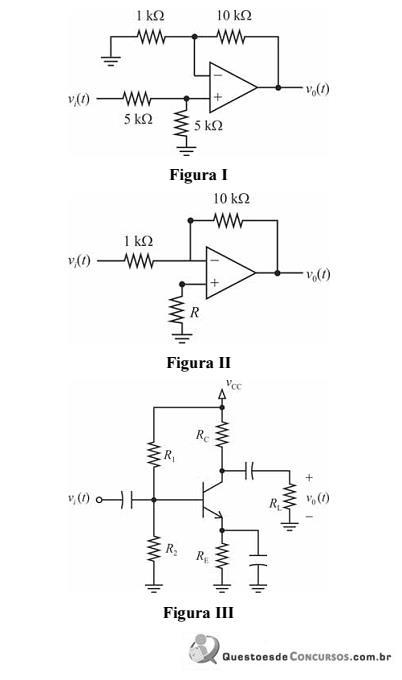

Dado o circuito com amplificadores operacionais apresentado, quando a tensão do sinal de entrada for Vin = - 50 mV, a saída Vout corresponderá a

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se, na entrada do conversor A/D, o sinal tiver amplitude de 2 V eficaz e a relação sinal-ruído (SNR) for de 40 dB, então o amplificador terá ganho G igual a 2.000 e a amplitude do ruído será inferior a 10 mV eficaz.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se a tensão de referência do conversor A/D for Vref = 5 V, então a resolução correspondente será inferior a 2 mV.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Para que o conversor A/D não distorça o sinal de entrada, é necessário que a taxa de amostragem mínima seja de 2 × 106 amostras por segundo.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Considere que a resposta em frequência da associação entre buffer e amplificador seja máxima e constante na faixa espectral compreendida entre 1 kHz e 500 MHz. Considere, ainda, que a banda passante dessa associação seja ajustável e possa ser selecionada entre dois valores: 200 MHz e 400 MHz. Nessa situação, a SNR será mínima se o valor de 200 MHz for escolhido para a largura de faixa da associação.

Em relação às eletrônicas analógica, digital e de potência, julgue o item seguinte.

O rendimento do amplificador classe C é maior que o dos

amplificadores classes A, B e AB, de modo que seu ganho é

máximo na frequência de ressonância.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura I, o ganho de tensão da entrada para a saída é igual a 10.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura III, como o transistor está operando na região ativa, ambas as junções base-emissor e coletor-base estão polarizadas diretamente.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

O amplificador ilustrado na figura III está na configuração coletor comum e possui ganho unitário.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura II, se um capacitor com capacitância de 100 nF for adicionado em paralelo com o resistor de resistência 10 kΩ, então o circuito terá uma resposta em frequência do tipo passa-baixa, cuja frequência de corte é superior a 10 Hz.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura II, a razão entre a tensão de saída e a de entrada é igual a -10.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

A impedância de saída do amplificador realimentado mostrado na figura I é igual a 10 kΩ.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura I, a impedância de entrada vista pela fonte de tensão vi(t) é igual a 5 kΩ.