Questões de Concurso

Sobre programação ladder em engenharia eletrônica

Foram encontradas 87 questões

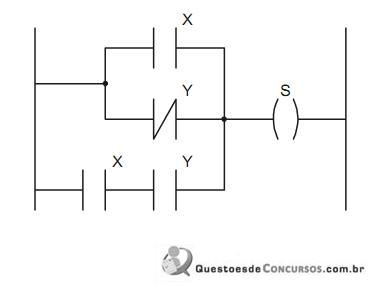

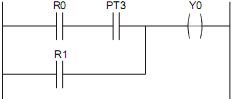

Para manter a mesma lógica, esse trecho pode ser substituído por:

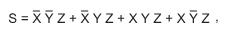

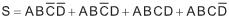

A expressão equivalente à saída S é:

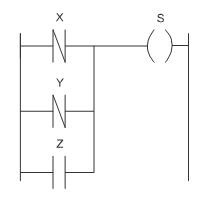

Ele executa a função lógica:

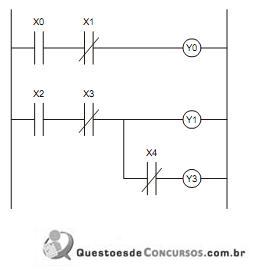

A lógica de acionamento de Y3 é

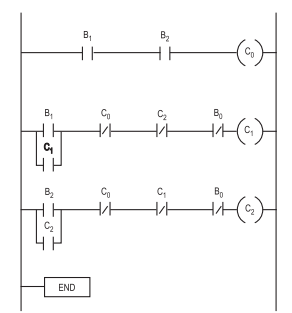

Considere o esquema LADDER de controle de um processo industrial apresentado na figura acima. O usuário tem acesso ao sistema de controle através das botoeiras denominadas B1'B2B0. Com base nessas informações e no diagrama apresentado, tem-se que a(s)

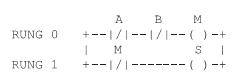

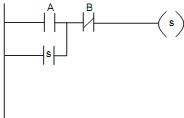

O programa em Ladder acima aciona a bobina S, obedecendo às condições dos contatos A e B. A expressão lógica correspondente ao programa é

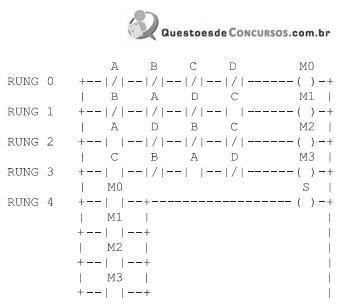

O programa em Ladder acima aciona a bobina S, obedecendo às condições dos contatos A, B, C e D. A simplificação desse programa está em

a lógica de programação Ladder correspondente é

, a lógica de programação Ladder correspondente é

, a lógica de programação Ladder correspondente é

A expressão lógica que o representa é:

O CLP é um computador dedicado ao controle e à automação de sistemas. Para programá-lo, o diagrama ladder (diagrama de relés) é muito utilizado. Acerca desse assunto, julgue o item seguinte.

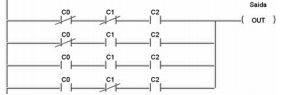

A saída do CLP a seguir é independente dos estados lógicos de C0 e de C1.

O CLP é um computador dedicado ao controle e à automação de sistemas. Para programá-lo, o diagrama ladder (diagrama de relés) é muito utilizado. Acerca desse assunto, julgue o item seguinte.

O diagrama abaixo apresenta três entradas (C0, C1 e C2) e uma saída. A saída desse diagrama tem nível lógico alto somente se duas ou mais dessas entradas também têm nível lógico alto.

A figura a seguir apresenta, em condições ideais de funcionamento, uma programação em linguagem de contatos (ou LADDER) em que o contato normalmente aberto B é energizado por uma botoeira (por cerca de um segundo) e os contatos definidos como D estão associados a uma chave.

No esquema: T0 e T1 são temporizadores e estão associados aos tempos de t1 s e t2 s, com t2 > t1; e M0, M1 e M2 são motores. O contato D está desligado e só é acionado após os três motores estarem em funcionamento.

C. Killian, Modern control technology: components and

systems. 2.o ed. Thompson, 2002 (com adaptações).

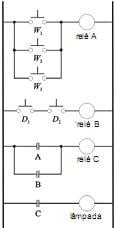

A figura acima mostra o diagrama lógico em linguagem ladder de um sistema simples de automação residencial para o monitoramento de três janelas e duas portas. Cada uma dessas janelas e portas têm um sensor de contato acoplado que é ativado quando a janela ou porta é aberta. No diagrama, {

} e {

} e { } são os contatos das janelas e das portas, respectivamente, sendo considerados contatos do tipo normalmente aberto. Com base nessas informações, é correto afirmar que

} são os contatos das janelas e das portas, respectivamente, sendo considerados contatos do tipo normalmente aberto. Com base nessas informações, é correto afirmar que

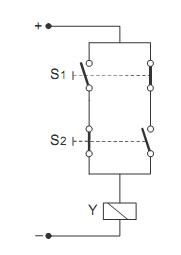

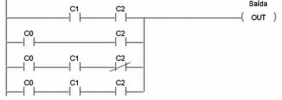

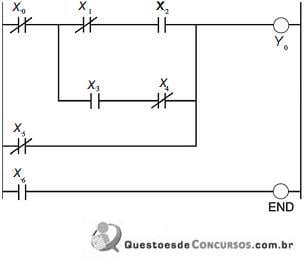

A figura acima mostra o diagrama ladder para um controlador lógico programável (CLP) genérico, em que {

} são as variáveis de entrada e

} são as variáveis de entrada e  é a variável de saída — essas variáveis podem assumir os valores lógicos verdadeiro e falso.

é a variável de saída — essas variáveis podem assumir os valores lógicos verdadeiro e falso. A saída na bobina,

, estará ativa — isto é, assumirá o valor lógico verdadeiro — se

, estará ativa — isto é, assumirá o valor lógico verdadeiro — se

Com a mudança de estado do bit A, a função do bit S, em paralelo com o bit A, é