Questões de Arquitetura de Computadores - Memória para Concurso

Foram encontradas 1.094 questões

Sobre Organização de Computadores, considere as seguintes afirmações:

I. Registradores são dispositivos de armazenamento internos à CPU, que podem ser lidos e escritos em alta velocidade e que se situam no topo da hierarquia de memória.

II. Os componentes de um computador são conectados por meio de barramentos de dados, endereço e controle.

III. A unidade de controle de uma CPU é responsável por buscar instruções na memória secundária e determinar seu tipo.

Está CORRETO o que se afirma em

Acerca de arquitetura de computadores, julgue o item a seguir.

Na DMA (direct memory access), que é uma das técnicas

de entrada/saída (E/S), a E/S é controlada por um

processador especializado que se incumbe de realizar a

transferência dos blocos de dados.

Acerca de arquitetura de computadores, julgue o item a seguir.

O tempo de acesso, em uma memória de acesso

aleatório, é definido como o tempo gasto para

posicionar o mecanismo de leitura/escrita na posição

desejada.

Acerca de arquitetura de computadores, julgue o item a seguir.

A memória flash é um tipo de memória volátil e apenas

de escrita.

A memória de um computador é organizada em uma estrutura hierárquica composta de múltiplos níveis: memória principal, memória cache e registradores. Considere um sistema computacional com palavra de dados de 32 bits e que possua um único nível de memória cache, com caches de instrução e de dados separadas, cada uma com capacidade de 16 palavras (64 Bytes). Analise as seguintes assertivas e assinale a alternativa correta:

I. A memória cache promove ganho de desempenho na execução de um programa apenas quando este exibe algum nível de localidade no acesso às instruções e/ou dados.

II. Se a cache de dados for baseada no mapeamento direto, para se obter uma maior taxa de acertos na execução de um programa com alta localidade espacial no acesso a dados, é melhor organizar essa cache em 16 blocos com 01 palavra/bloco do que em 04 blocos com 04 palavras/bloco.

III. Para programas que exibam localidade temporal no acesso às instruções, para obter uma menor taxa de faltas, é melhor que a cache de instruções seja baseada no mapeamento associativo de duas vias do que no mapeamento direto. Isso se justifica porque o mapeamento associativo oferece alternativas de blocos para carregar uma posição da memória principal na cache e isso reduz a necessidade de substituição de blocos na cache.

No que concerne os componentes de um computador, considere as afirmações abaixo.

1) Um processador CISC reconhece centenas de instruções complexas, por isso é mais rápido que um processador RISC.

2) Um processador RISC reconhece um conjunto limitado de instruções. As instruções não contempladas são executadas como combinações das existentes.

3) A memória do tipo SRAM é extremamente rápida e, embora volátil, só perde seu conteúdo se a máquina for desligada, não exigindo que a CPU renove seu conteúdo continuamente.

4) Uma célula de memória é a menor unidade endereçável no computador. O termo palavra é usado para designar a quantidade de bits que pode ser armazenada em cada célula. Então, em uma máquina de 16 bits, cada célula da memória principal armazena 2 bytes.

5) Em uma máquina pipeline, a execução de uma instrução é dividida em diferentes estágios de modo que cada um deles seja manipulado por partes de hardware específicas.

Estão corretas:

Memórias DDR, DDR2 e DDR3 seguem uma classificação do tipo DDRxxx/PCyyyy.

DDRxxx é o padrão usado para classificar chips de memória e PCyyyy é o padrão usado para classificar módulos de memória. Na figura a seguir, você pode ver a identificação de um módulo de memória PC3- 10666 que usa chips de memória DDR3-1333.

Com base na figura acima, é CORRETO afirmar:

A tecnologia DDR é uma inovação da DRAM para aumentar o desempenho dos computadores. Analise as proposições a seguir a respeito da memória DDR e assinale a alternativa CORRETA.

A memória DDR possibilita dobrar a taxa de dados de pico.

PORQUE

A DDR transfere dados tanto na borda de subida quanto na borda de descida do sinal de clock da DRAM.

O uso de memória cache é imprescindível para o bom funcionamento dos processadores modernos.

Com relação às memórias caches, analise as afirmativas a seguir.

I. O uso de memórias síncronas (SDRAM) na memória principal permite a transferência em modo rajada de blocos de informação entre a memória cache e a memória principal.

II. Nos modernos processadores, como o processador Intel i7, a cache de nível 1 é utilizada para a comunicação entre as “threads” que são executadas em núcleos (“cores”) diferentes.

III. A cache dos processadores é construída com memórias estáticas, mais rápidas, em oposição ao uso de memórias dinâmicas na memória principal, que são mais lentas.

Está correto o que se afirma em

O chefe do setor explicou que os dois computadores disponíveis apresentam a mesma quantidade de memória RAM e 1TB de HD padrão SATA III. Porém, o computador instalado na primeira mesa possui um processador quad core AMD e placa de rede Wi-Fi. Já o computador novo, na segunda mesa, possui um processador quad core Intel e placa de rede Gigabit Ethernet.

Caso o técnico administrativo desejasse, havia a opção de acrescentar mais 4GB de memória DDR3 ao computador com processador AMD.

O chefe do setor explicou que os dois computadores disponíveis apresentam a mesma quantidade de memória RAM e 1TB de HD padrão SATA III. Porém, o computador instalado na primeira mesa possui um processador quad core AMD e placa de rede Wi-Fi. Já o computador novo, na segunda mesa, possui um processador quad core Intel e placa de rede Gigabit Ethernet.

Caso o técnico administrativo desejasse, havia a opção de acrescentar mais 4GB de memória DDR3 ao computador com processador AMD.

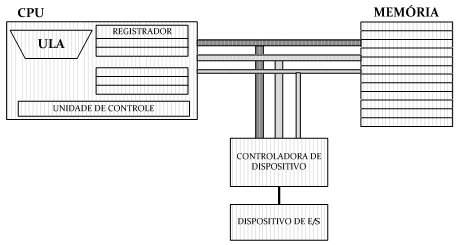

Um computador pode ser dividido em três grandes subsistemas: a CPU, a memória principal e o E/S. Considere a figura a seguir.

Sobre a figura, marque V para as proposições verdadeiras e F para as falsas.

( ) A interconexão desses subsistemas é feita por três barramentos: de dados, de endereços e de controle. O número de linhas no barramento de dados depende do tamanho das palavras usadas na arquitetura do computador; no barramento de endereço, o número de linhas depende do espaço de endereçamento da memória e, no barramento de controle, o número de linhas é dado pelo número de posições de memória.

( ) São controladores de dispositivos ou interfaces: USB, FireWire e SCSI.

( ) O endereçamento dos dispositivos de E/S pode ser feito utilizando-se de dois métodos: E/S isolada, isto é, existem instruções exclusivas para endereçar o dispositivo, ou E/S mapeada em memória.

( ) A operação de transferência de dados pode ser realizada por três métodos: E/S programada, E/S dirigida por interrupção e DMA.

Assinale a sequência correta.

Considere um computador de 64 bits, cujos endereços sequenciais de memória abaixo são válidos.

Endereço 1: 000000000022FE38

Endereço 2: 000000000022FE40

Endereço 3: 000000000022FE48

Endereço 4: 000000000022FE4C

Um Técnico em Informática conclui, corretamente, que