Questões de Concurso

Sobre memória em arquitetura de computadores

Foram encontradas 1.120 questões

Com relação a microcomputadores, julgue o item abaixo.

O acesso à memória no disco rígido, denominada memória

cache, é, em geral, mais rápido que o acesso à memória

principal do microcomputador, pois a memória principal é um

tipo de memória dinâmica e a memória do disco rígido, um

tipo de memória estática semicondutora de alta velocidade.

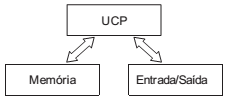

Exemplos de dispositivos e componentes utilizados em PCs para implementar a Memória e a Entrada/Saída da arquitetura são, respectivamente,

O número de bits do barramento de endereços necessário para endereçar todas as posições do circuito integrado de memória RAM é igual a 8 bits.

As memórias RAM desse tipo são, em sua maioria, do tipo dinâmica, dada a velocidade e a quantidade de memória requerida.

O tipo de memória RAM (random access memory) permite que os dados processados no computador fiquem armazenados mesmo quando o computador estiver desligado. Essa característica reside por tratar-se de uma memória randômica não volátil.

Com relação à figura acima, que ilustra um sistema com múltiplos processadores, na qual os símbolos triangulares, identificados de P1 a P9, representam processadores; os símbolos retangulares, identificados de M1 a M3, representam memórias; ao passo que as linhas que interligam esses conjuntos são barramentos.

A figura em tela representa a arquitetura de sistemas NUMA (non-uniform memory access), na qual o tempo de acesso à memória principal depende da localização física do processador, e todos os conjuntos compartilham o mesmo sistema operacional e referenciam o mesmo espaço de endereçamento.

Completa correta e respectivamente as lacunas

Julgue o item a seguir, acerca dos tópicos avançados em desenvolvimento de sistemas.

A arquitetura de memória compartilhada de sistema

multiprocessador é fortemente acoplada, pois múltiplos

processadores compartilham armazenamento secundário em

disco, mas cada processador possui sua própria memória

primária.

Acerca de um sistema microprocessado, julgue o item subsequente.

Memória cache é uma memória de acesso aleatório, ou random

access memory (RAM). Essa é normalmente menor e mais

rápida que a memória RAM dinâmica (DRAM) externa, que,

por sua vez, é normalmente menor e mais rápida que a

memória de massa.

A memória flash, que se constitui de uma pequena porção de memória com curto tempo de resposta, normalmente integrada aos processadores, permite incrementar o desempenho do processador durante a execução de um programa.