Questões de Concurso

Sobre modos de endereçamento em arquitetura de computadores

Foram encontradas 98 questões

computacional, julgue os itens subsequentes.

MOV R1, A(R2)

I - Esse computador tem a capacidade de armazenar 5.120 kbits.

II - O registrador de dados da memória armazena 10 bits e a barra de dados também permite a passagem de 10 bits simultaneamente.

III - O registrador de endereço de memória e a barra de endereços armazenam, no mínimo, 9 bits para que seja possível o acesso a todas as posições de memória.

Está(ão) correta(s) a(s) afirmação(ões)

36 a 40.

para emprego geral, denominado ENIAC (electronic numerical

integrator and computer), foi projetado por John Mauchly e John

P. Eckert, de 1943 a 1946. Daí em diante, a arquitetura dos

computadores tem mudado constantemente. Em relação aos

componentes funcionais (hardware) de um computador, julgue os

itens a seguir

Considerando a figura acima, que apresenta diferenças no uso de esquemas de endereçamento de memória em ambientes OS/400 e NT ou UNIX, julgue os próximos itens, a respeito de conceitos de arquitetura de grande porte.

Considerando a figura acima, que apresenta diferenças no uso de esquemas de endereçamento de memória em ambientes OS/400 e NT ou UNIX, julgue os próximos itens, a respeito de conceitos de arquitetura de grande porte.

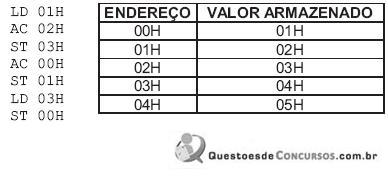

LD : Copia da memória principal para o registrador R.

AC: Adiciona da memória principal ao registrador R.

ST: Move do registrador R para a memória principal.

Considere o programa apresentado abaixo, executado no computador, acessando o bloco de memória principal, cuja situação inicial é mostrada a seguir.

Considere que tanto o endereçamento quanto os valores envolvidos nas operações utilizam apenas um byte de memória cada. Após a execução do programa, qual será, em hexadecimais, a soma dos valores armazenados no bloco de memória?

Considerando a figura acima, que apresenta um diagrama de

blocos da arquitetura de um computador pessoal, julgue os itens

subseqüentes acerca de conceitos de informática.

I. Em uma placa-mãe, as entradas padrão PCI servem para se encaixar os cabos que ligam unidades de CD/ DVD. Esses cabos, chamados de fl at cables, podem ser de 40 ou 80 vias. Cada cabo pode suportar até duas unidades de CD/DVD.

II. O endereçamento consiste na capacidade do processador de acessar um número máximo de células da memória. Para acessar uma célula, o processador precisa saber o endereço dela. Cada célula armazena um byte. Assim, um processador com o barramento de dados com 16 bits pode acessar duas células por vez.

III. O clock interno indica a freqüência na qual o processador trabalha. Portanto, num Pentium 4 de 2,6 GHz, o "2,6 GHz" indica o clock interno, geralmente obtido por meio de um multiplicador do clock externo. O clock externo é o que indica a freqüência de trabalho do barramento de comunicação com a placa-mãe.

IV. O setor de BOOT de um HD contém um pequeno software chamado Post, que é responsável por controlar o uso do hardware do computador, manter as informações relativas à hora e data e testar os componentes de hardware após o computador ser ligado.

Indique a opção que contenha todas as afirmações verdadeiras.

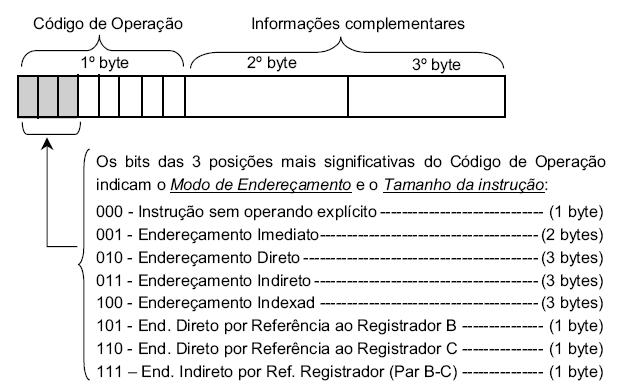

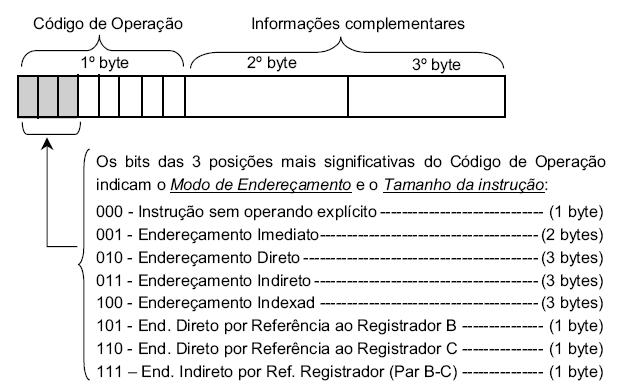

- Todas as instruções usam o Acumulador com 1o operando (implícito) e têm o seguinte significado: "Carregar o Acumulador com o 2o operando, explicitado pelo modo de endereçamento indicado pela instrução".

- Os endereços são armazenados na Memória Principal com sua parte mais significativa na célula de endereço mais alto.

- As memórias locais foram previamentre carregadas com os conteúdos abaixo: Registrador de índice: 02H; Registrador B: 23H; Registrador C: 14H.

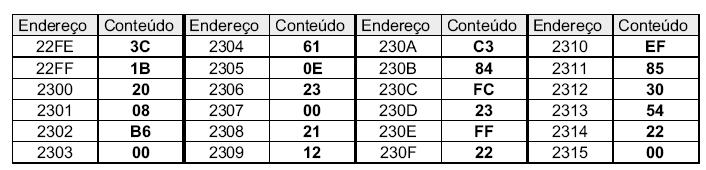

Considere o trecho da Memória Principal deste computador, mostrado na tabela abaixo.

Quando o CI=2304, qual será o conteúdo do Acumulador após o processamento da instrução?