Questões de Concurso Sobre arquitetura de computadores

Foram encontradas 6.340 questões

Acerca de arquitetura de computadores, julgue o item a seguir.

Um barramento é um meio de comunicação ao qual

vários dispositivos podem ser conectados, sendo

caracterizado como um meio de transmissão

compartilhado.

A memória de um computador é organizada em uma estrutura hierárquica composta de múltiplos níveis: memória principal, memória cache e registradores. Considere um sistema computacional com palavra de dados de 32 bits e que possua um único nível de memória cache, com caches de instrução e de dados separadas, cada uma com capacidade de 16 palavras (64 Bytes). Analise as seguintes assertivas e assinale a alternativa correta:

I. A memória cache promove ganho de desempenho na execução de um programa apenas quando este exibe algum nível de localidade no acesso às instruções e/ou dados.

II. Se a cache de dados for baseada no mapeamento direto, para se obter uma maior taxa de acertos na execução de um programa com alta localidade espacial no acesso a dados, é melhor organizar essa cache em 16 blocos com 01 palavra/bloco do que em 04 blocos com 04 palavras/bloco.

III. Para programas que exibam localidade temporal no acesso às instruções, para obter uma menor taxa de faltas, é melhor que a cache de instruções seja baseada no mapeamento associativo de duas vias do que no mapeamento direto. Isso se justifica porque o mapeamento associativo oferece alternativas de blocos para carregar uma posição da memória principal na cache e isso reduz a necessidade de substituição de blocos na cache.

Qual alternativa melhor explica o que vai acontecer?

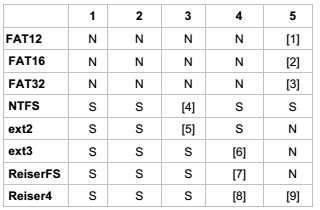

Considere os sistemas de arquivos FAT12, FAT16, FAT32, NTFS, EXT2, EXT3 e REISER. Substitua as entradas numeradas de [1] a [9] na tabela abaixo com “S” ou “N” conforme o sistema de arquivos na linha correspondente tenha (S) ou não (N) a característica na coluna. Onde as características estão assim numeradas:

1) Hard Links

2) Soft Links

3) Block Journalling

4) Cas-Sensitive

5) File Change Log

Por exemplo FAT12 Não tem a característica 3 que é ter

Block Journalling. Assinale a sequência de N's e S's correta

abaixo:

No que concerne os componentes de um computador, considere as afirmações abaixo.

1) Um processador CISC reconhece centenas de instruções complexas, por isso é mais rápido que um processador RISC.

2) Um processador RISC reconhece um conjunto limitado de instruções. As instruções não contempladas são executadas como combinações das existentes.

3) A memória do tipo SRAM é extremamente rápida e, embora volátil, só perde seu conteúdo se a máquina for desligada, não exigindo que a CPU renove seu conteúdo continuamente.

4) Uma célula de memória é a menor unidade endereçável no computador. O termo palavra é usado para designar a quantidade de bits que pode ser armazenada em cada célula. Então, em uma máquina de 16 bits, cada célula da memória principal armazena 2 bytes.

5) Em uma máquina pipeline, a execução de uma instrução é dividida em diferentes estágios de modo que cada um deles seja manipulado por partes de hardware específicas.

Estão corretas:

A execução de um programa retornou um erro de acesso a memória de endereço 567. Considere as afirmações sobre conversão entre bases:

1) Se 765 estiver na base hexadecimal, em binário é 11101100101.

2) Se 765 estiver na base octal, em binário é 111110101.

3) A soma do decimal correspondente ao binário da afirmação 1 com o o decima do binário da afirmação 2, é igual ao dobro do decimal 765.

Está(ão) correta(s):

A typical computer system provides a hierarchy of different types of memories for data storage. Consider the statements below.

I. The hard drive has a local data cache. Because the hard drive access speed is so much slower, disk access are normally done asynchronously at the hardware level. The hard drive controller will acknowledge the instruction right away, and will take sometime to populate the disk cache with the requested data block, and then, at a later time, raise an interrupt to notify the interested party that the data access is complete. This model of interrupt based data transfer is asynchronous.

II. The cache is made up of small chunks of mirrored main memory. The size of these chunks is called the line size, and is typically something like 32 or 64 bytes. The cache can load and store memory in sizes a multiple of a cache line. Caches have their own hierarchy, commonly termed L1, L2 and L3. L1 cache is the fastest and smallest; L2 is bigger and slower, and L3 more so.

III. Internal register in a CPU is used for holding variables and temporary results. Internal registers have a very small storage; however they can be accessed instantly. Accessing data from the internal register is the fastest way to access memory. Most registers are implemented as an array of DRAM cells. DRAM is a type of RAM that is much faster and more reliable than the SRAM, which is used for main memory because of its lower cost and smaller space consumption. DRAM does not need to be electrically refreshed as does SRAM.

The correct statement (s)

Dentre as operações de aritmética computacional em binário e hexadecimal há a multiplicação e a divisão pela base. Uma operação deste tipo cujo resultado está corretamente calculado é: