Questões de Concurso Sobre arquitetura de computadores

Foram encontradas 6.341 questões

As lacunas de I a III são preenchidas corretamente e respectivamente com:

I. Contemplam componentes como controladores e coprocessadores. Têm um conjunto de instruções (de propósito geral ou especializado) operando sobre instruções e dados.

II. Incluem dois subsistemas: principal e secundário. O custo associado está diretamente relacionado à sua capacidade de armazenamento e à sua velocidade de operação.

III. São conversores de representação física de dados. Em geral, são lentos quando comparados com o processador.

Os itens de I a III se referem, respectivamente, a

O custo de armazenamento de dados em discos rígidos magnéticos ou em discos de estado sólido é muito baixo atualmente. Assim, as soluções de armazenamento em que se utilizam fitas e fitotecas automatizadas tornaram-se obsoletas, visto que estas podem ser completamente substituídas, em qualquer cenário, por soluções de armazenamento em disco.

Os mainframes IBM recentes possuem, em sua arquitetura de hardware, não apenas uma CPU (central processing unit), mas também um CPC (central processor complex), o qual pode conter diferentes tipos de processadores a serem utilizados para diferentes propósitos.

A arquitetura RISC (reduced instruction set computer) busca reduzir o número de ciclos necessários para que uma instrução seja executada, sendo amplamente utilizada em processadores que têm por base o conjunto de instruções x86, desde as primeiras versões desses processadores.

A abordagem da arquitetura CISC (complex instruction set computer) procura minimizar o número de ciclos para que uma instrução seja executada, e aumenta, em contrapartida, o número de instruções por programa.

Uma finalidade do uso da alocação aleatória de endereços é evitar a execução arbitrária de código.

01011010 10000111 b

Esse número binário, na notação hexadecimal, é:

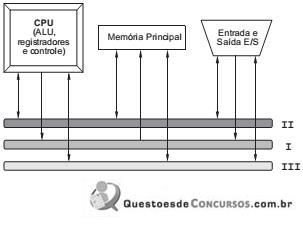

A CPU gera endereços que são colocados no barramento ...I.....e a memória os recebe através deste barramento. O caminho inverso desta operação não é possível (isso pode ser observado na figura). Durante a execução de um programa, cada instrução é levada até a ALU a partir da memória, uma instrução de cada vez, junto com qualquer dado que seja necessário para executá- la, cujo valor é transmitido através do barramento...II.... . A saída do programa é colocada em um dispositivo como um monitor de vídeo ou disco. A comunicação entre os componentes do sistema é sincronizada pelo barramento...III.. .

As lacunas I, II e III são correta e, respectivamente, preenchidas por:

Em uma arquitetura computacional, o modo de endereçamento em bytes exige que o conteúdo de dados alocados nos registradores seja, obrigatoriamente, múltiplo de 8 bits.

Mediante a unidade lógica aritmética (ULA), realizam-se operações única e exclusivamente entre os conteúdos de registradores, independentemente da arquitetura e da organização computacional utilizada.