Questões de Concurso Público TRE-BA 2010 para Técnico Judiciário - Telecomunicações e Eletricidade

Foram encontradas 31 questões

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue o item que se segue.

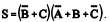

Considerando-se a forma soma de produtos, a expressão

booleana mínima para a saída S é dada por

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue o item que se segue.

Na forma produto de somas, a expressão booleana mínima para

a saída S é dada por

A tabela verdade acima descreve um circuito combinacional com entradas A, B e C, e saída S. Com relação a essa tabela, julgue o item que se segue.

Embora não seja a expressão booleana mínima para a saída S,

a expressão booleana  expressa corretamente a saída S em função das entradas A, B

e C.

expressa corretamente a saída S em função das entradas A, B

e C.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se as entradas A, B, C, D e E assumirem, respectivamente, os

valores 1, 1, 0, 1 e 1, então a saída S assumirá o valor 1.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se a entrada E assumir o valor 1, então a saída S assumirá o

valor 1, independentemente dos valores assumidos pelas

variáveis A, B, C e D.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se as portas TTL usadas no circuito forem do tipo HS, elas

terão um tempo de comutação, de um estado para outro, muito

maior do que se as portas forem do tipo LS, e o consumo de

potência das portas do tipo HS será menor do que o consumo

das portas do tipo LS.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

A expressão lógica resultando na saída S = [AB + (A+B)]E

descreve corretamente a relação entre a saída e as entradas do

circuito.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

O circuito utiliza uma porta lógica do tipo ou exclusivo.

Com relação a sistemas e dispositivos digitais, julgue o item seguinte.

No flip-flop JK do tipo mestre-escravo, se as entradas J e K

estiverem todo o tempo conectadas ao nível lógico 1, então a

saída Q, após sucessivos ciclos de relógio, permanecerá no

nível lógico 1.

Com relação a sistemas e dispositivos digitais, julgue o item seguinte.

Em uma memória ROM de 2 kilobytes, 11 bits de endereços

são suficientes para permitir o endereçamento de todas as

posições de memória.

Acerca dos dispositivos eletrônicos, julgue o próximo item.

O transistor de unijunção (UJT) é um dispositivo de três

terminais. O silício pode ser utilizado na construção desse tipo

de componente.

Acerca dos dispositivos eletrônicos, julgue o próximo item.

O retificador controlado de silício (SCR) é um dispositivo de

três terminais que contém apenas uma região do tipo p e duas

regiões do tipo n, que formam um total de duas junções PN. Os

três terminais desse dispositivo são denominados porta, dreno

e fonte.

Acerca dos dispositivos eletrônicos, julgue o próximo item.

No fotodiodo, o número de elétrons livres gerados em cada

material semicondutor que o compõe é inversamente

proporcional à intensidade da luz incidente no dispositivo.

Essa sensibilidade permite que o diodo seja usado em

aplicações que requeiram um sensor de luminosidade.

A figura acima ilustra a estrutura básica de um controlador lógico programável (CLP). A respeito dessa estrutura e do funcionamento de um CLP, julgue o item a seguir.

Os sinais de entrada e saída, como na estrutura mostrada,

podem ser digitais, mas somente os de entrada podem ser

analógicos.

A figura acima ilustra a estrutura básica de um controlador lógico programável (CLP). A respeito dessa estrutura e do funcionamento de um CLP, julgue o item a seguir.

Na unidade central de processamento (UCP), os cartões de

entrada e de saída são os elementos responsáveis pelo

processamento das informações do CLP. Para essa finalidade,

esses componentes fazem uso de dados que são armazenados

em memórias específicas localizadas na UCP.

Em um enlace de comunicação por fibra óptica, utiliza-se um diodo laser de comprimento de onda igual a 500 nm e potência de onda contínua (CW) igual a 5 mW. O feixe laser é acoplado a uma fibra óptica circular de índice degrau, com abertura numérica NA = 0,21 e atenuação de potência Ad = 1,249 dB/km para uma frequência de operação de 600 THz. Considerando essas informações, julgue o item que se segue.

A fibra óptica apropriada para ocorrência de propagação monomodo tem diâmetro superior a 5 μm.

Em um enlace de comunicação por fibra óptica, utiliza-se um diodo laser de comprimento de onda igual a 500 nm e potência de onda contínua (CW) igual a 5 mW. O feixe laser é acoplado a uma fibra óptica circular de índice degrau, com abertura numérica NA = 0,21 e atenuação de potência Ad = 1,249 dB/km para uma frequência de operação de 600 THz. Considerando essas informações, julgue o item que se segue.

Considerando a aproximação 10-0,1 = 0,794 e desprezando

perdas no mecanismo de acoplamento laser/fibra, é correto

afirmar que, para um enlace com 600 m de fibra óptica, a

potência do feixe laser detectado na saída da fibra é superior

a 4 mW.

Um esquema para detecção de dados é a paridade, uma técnica utilizada para detecção de ocorrência de erros em uma transmissão digital de sinais. O circuito acima foi projetado para examinar os bits 1 de cada palavra digital transmitida e produzir bit 1 ou 0 adicional para que o total de bits 1 resulte par (paridade par) ou ímpar (paridade ímpar). O mesmo circuito pode ser usado para verificação de paridade no receptor: nesse local, caso a verificação de paridade seja falsa, significa que ocorreu um erro de transmissão. Nesse esquema específico, a palavra digital de sete bits é acoplada, bit a bit, nas entradas de e1 a e7. Os bits adicionais, disponíveis nos terminais Pi e Po, determinam a paridade da palavra digital. De acordo com essas informações e com a figura apresentada acima, julgue o próximo item.

Para que o circuito funcione como gerador de paridade, o

terminal Pi

deve ser ligado ao terra do circuito, para geração de

paridade ímpar, ou à fonte de alimentação do circuito, para

geração de paridade par.

Um esquema para detecção de dados é a paridade, uma técnica utilizada para detecção de ocorrência de erros em uma transmissão digital de sinais. O circuito acima foi projetado para examinar os bits 1 de cada palavra digital transmitida e produzir bit 1 ou 0 adicional para que o total de bits 1 resulte par (paridade par) ou ímpar (paridade ímpar). O mesmo circuito pode ser usado para verificação de paridade no receptor: nesse local, caso a verificação de paridade seja falsa, significa que ocorreu um erro de transmissão. Nesse esquema específico, a palavra digital de sete bits é acoplada, bit a bit, nas entradas de e1 a e7. Os bits adicionais, disponíveis nos terminais Pi e Po, determinam a paridade da palavra digital. De acordo com essas informações e com a figura apresentada acima, julgue o próximo item.

Para uma verificação válida (verdadeira), a fim de que o

circuito funcione como um verificador de paridade ímpar, o bit

correspondente ao terminal Po deverá ser 0.

Medidas realizadas na saída de um receptor de dados binários foram utilizadas para gerar a curva linear, que mostra como varia a probabilidade de erro (Per) versus a relação sinal ruído (SNR). Com base na análise da curva linear representada na figura acima, julgue o item subsequente.

Considerando uma relação SNR de 12 dB, o número de erros

esperados em uma mensagem de 100 Mbits será superior a

100.