Questões de Concurso Público STF 2013 para Analista Judiciário - Engenharia Elétrica

Foram encontradas 31 questões

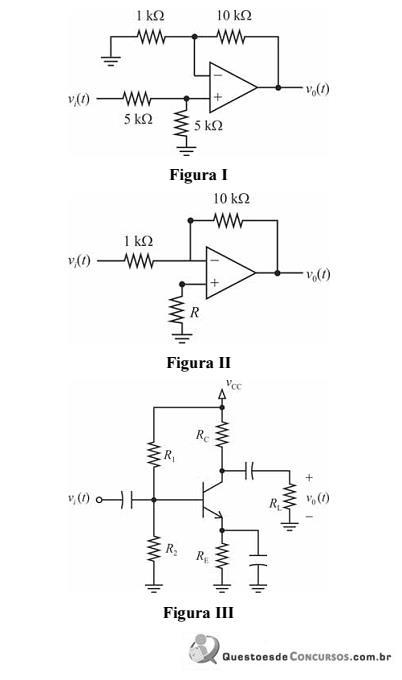

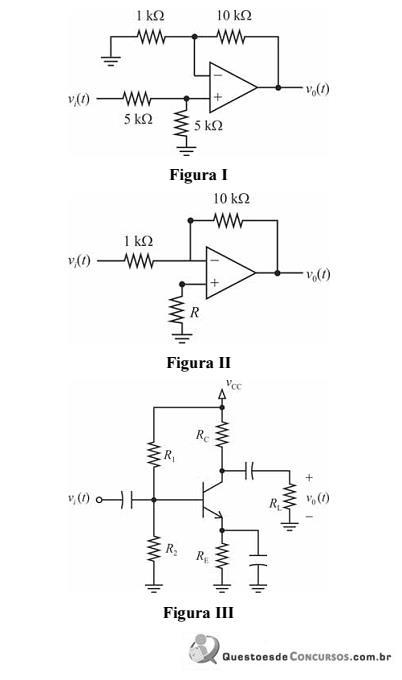

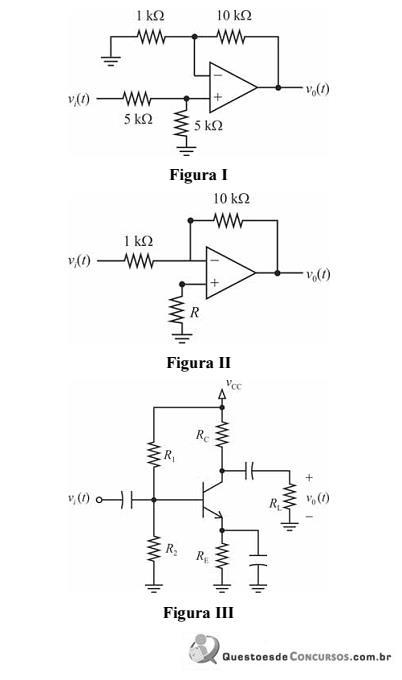

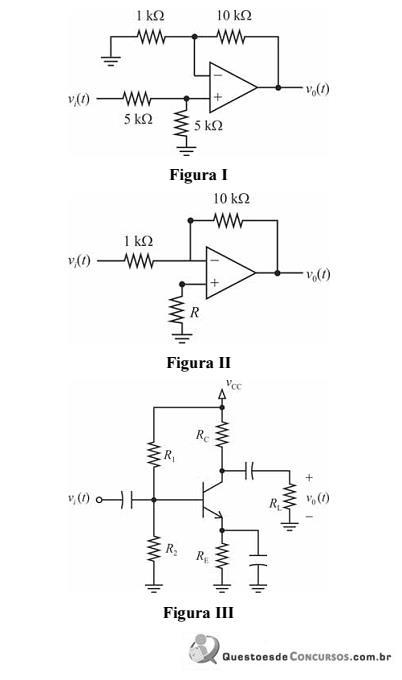

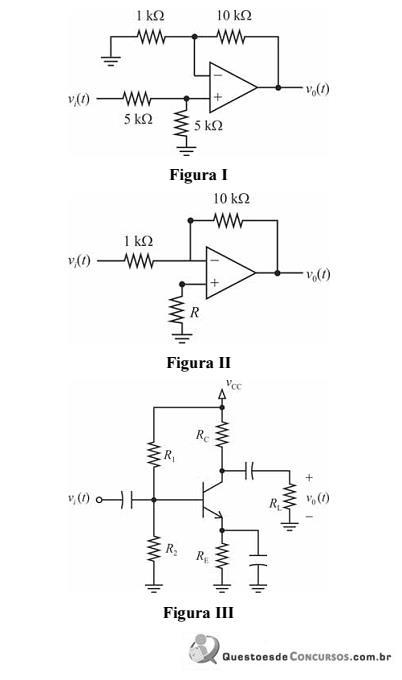

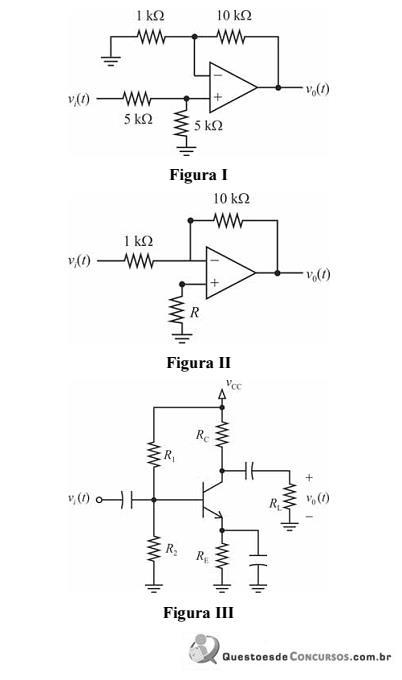

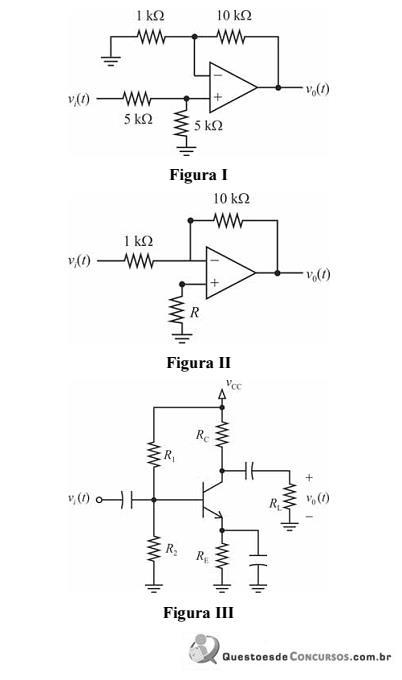

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura I, a impedância de entrada vista pela fonte de tensão vi(t) é igual a 5 kΩ.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

A impedância de saída do amplificador realimentado mostrado na figura I é igual a 10 kΩ.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura II, a razão entre a tensão de saída e a de entrada é igual a -10.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura II, se um capacitor com capacitância de 100 nF for adicionado em paralelo com o resistor de resistência 10 kΩ, então o circuito terá uma resposta em frequência do tipo passa-baixa, cuja frequência de corte é superior a 10 Hz.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

O amplificador ilustrado na figura III está na configuração coletor comum e possui ganho unitário.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura III, como o transistor está operando na região ativa, ambas as junções base-emissor e coletor-base estão polarizadas diretamente.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura I, o ganho de tensão da entrada para a saída é igual a 10.

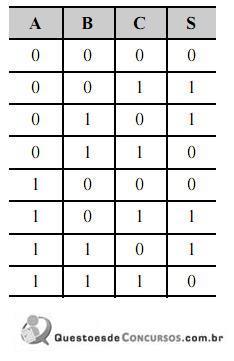

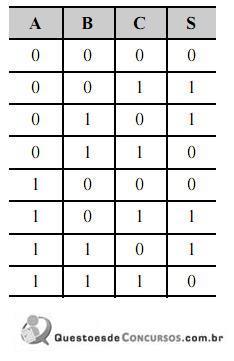

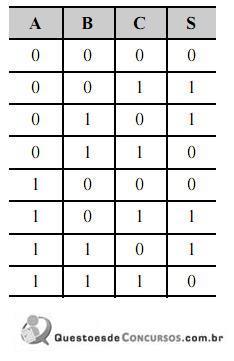

Considerando a tabela-verdade mostrada acima, que descreve o funcionamento de um circuito digital com entradas A, B e C, e saída S, julgue o item seguinte.

Entre todas as famílias lógicas, a família ECL é a que permite implementar o circuito digital relativo à tabela-verdade em apreço com o menor consumo de potência, porém, com menor velocidade de comutação.

Considerando a tabela-verdade mostrada acima, que descreve o funcionamento de um circuito digital com entradas A, B e C, e saída S, julgue o item seguinte.

A expressão lógica mínima para a saída S, na forma de soma de produtos, é

Considerando a tabela-verdade mostrada acima, que descreve o funcionamento de um circuito digital com entradas A, B e C, e saída S, julgue o item seguinte.

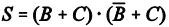

A expressão lógica mínima para a saída S, na forma de produto de somas, é

.

. Em um conversor digital-analógico que utilize uma rede R-2R, a dependência da precisão do conversor relativamente à precisão dos resistores será muito maior que a de um conversor digital-analógico que utilize uma rede de resistores ponderados em que os valores dos resistores cresçam como uma série geométrica com razão 2.

Se um conversor analógico-digital tiver entrada analógica entre 0 V e 5 V e saída de 8 bits que formem números entre 0 e 255, então uma entrada de 2 V corresponderá à saída 102.

Na expansão em frações parciais da função de transferência Y (S) = - (S2 + S - 1)/ S (S + 1)(S + 2) o coeficiente da parcela do polo real igual a -1 será maior que 3.

Um sistema cuja resposta ao impulso seja dada pela função h(t) = e-t sen(3t), em que t é uma variável temporal contínua, será instável em regime permanente.

Durante a conversão analógica-digital de um sinal, a etapa de codificação tem como propósito representar cada amostra quantizada por meio de uma palavra digital com um número finito de símbolos.

A convolução entre os sinais e x(t) = 1 e y(t) = e-t , que sejam avaliados somente para t

0, será igual a z(t) = 1 - e-t .

0, será igual a z(t) = 1 - e-t . Durante a realização do processo para aquisição de um sinal, a etapa de quantização é seguida pela etapa de amostragem.

O sistema representado por G(s) é controlável.

O ganho DC da função de transferência G(s) é menor que 2.

O pico de ressonância representa o valor máximo da magnitude da resposta em frequência de um sistema linear em malha- fechada.