Questões de Concurso Público INPE 2024 para Tecnologista Pleno I - Desenvolvimento de Sistemas de Suprimento de Energia para Satélites

Foram encontradas 30 questões

Existem diversas técnicas para sintonia dos parâmetros desse tipo de controlador, a qual deve ser escolhida de acordo com as características do sistema como um todo.

Uma destas técnicas é o método

( ) A sequência das etapas na conversão analógico-digital ocorre na seguinte ordem: codificação, amostragem e quantização.

( ) A taxa de bits mínima necessária para a digitalização de um sinal de voz, com uma largura de banda de 4 kHz com um quantizador uniforme de 1024 níveis, é de 8192 kbps.

( ) O filtro anti-aliasing é implementado após a fase de amostragem para diminuir ou suprimir as componentes de alta frequência do sinal. A presença dessas frequências elevadas pode resultar em distorções devido à sobreposição das réplicas do sinal amostrado, fenômeno conhecido como aliasing.

As afirmativas são, respectivamente,

Em relação aos parâmetros dos MOSFET de potência na situação acima mencionada, assinale a afirmativa correta.

Sobre o PWM, assinale a afirmativa correta.

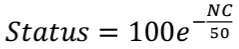

Considere que essa propriedade seja dependente exclusivamente do número de cargas (NC) e possa ser aproximada pela equação

Em que:

• NC é o número de cargas; e

• Status da bateria.

De acordo com as especificações, a bateria deverá ser substituída quando seu Status for menor que 50.

Dados:

Diante do exposto, o número máximo de cargas a que a bateria poderá ser submetida antes da substituição é

Considerando que o conversor opere em modo de condução contínuo e que a razão de trabalho de chaveamento (ou ciclo de trabalho) é 0,4, a corrente média de saída, em A, é

Sabe-se que, nesse projeto, a tensão da fonte de alimentação é 120 V, a tensão queda de tensão entre coletor e emissor do IGBT é 4 V e a corrente média da carga é 2,32 A.

Diante do exposto, o ciclo de trabalho do circuito de chaveamento, em valores percentuais, é

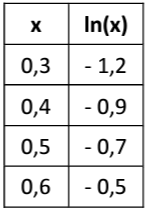

As lógicas das saídas A<B e A=B do comparador unsigned do circuito acima são, respectivamente,

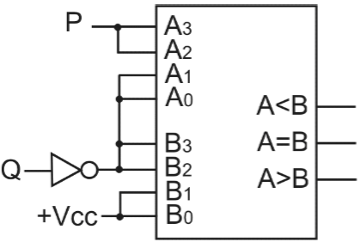

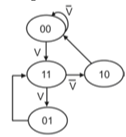

Após um pulso de CLR em nível baixo e mais de 30 pulsos de CLK, sem que ocorra novo pulso de CLR, o estado QBQA do circuito da figura acima, composto por dois flip-flops, dois inversores e mais uma porta lógica, ficará

A lógica de menor soma de produtos a ser usada para acionar DB é