Questões de Concurso Público INPE 2024 para Tecnologista Pleno I - Desenvolvimento de Sistemas de Suprimento de Energia para Satélites

Foram encontradas 6 questões

É correto afirmar que

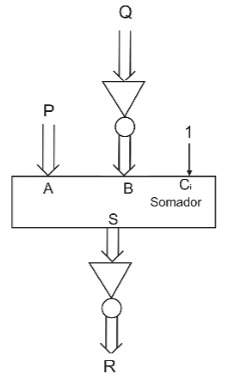

O valor esperado da tensão na entrada do conversor e o valor aproximado da maior tensão positiva que o conversor pode representar, estão, respectivamente, entre

( ) A sequência das etapas na conversão analógico-digital ocorre na seguinte ordem: codificação, amostragem e quantização.

( ) A taxa de bits mínima necessária para a digitalização de um sinal de voz, com uma largura de banda de 4 kHz com um quantizador uniforme de 1024 níveis, é de 8192 kbps.

( ) O filtro anti-aliasing é implementado após a fase de amostragem para diminuir ou suprimir as componentes de alta frequência do sinal. A presença dessas frequências elevadas pode resultar em distorções devido à sobreposição das réplicas do sinal amostrado, fenômeno conhecido como aliasing.

As afirmativas são, respectivamente,

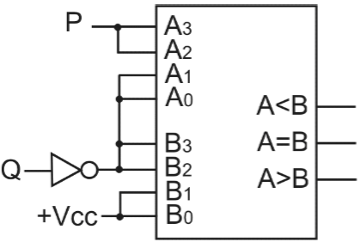

As lógicas das saídas A<B e A=B do comparador unsigned do circuito acima são, respectivamente,

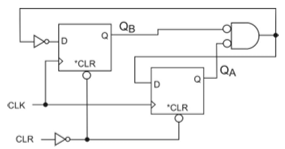

Após um pulso de CLR em nível baixo e mais de 30 pulsos de CLK, sem que ocorra novo pulso de CLR, o estado QBQA do circuito da figura acima, composto por dois flip-flops, dois inversores e mais uma porta lógica, ficará