Questões de Concurso Sobre plc em engenharia eletrônica

Foram encontradas 123 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

NÃO faz parte desse ciclo a(o)

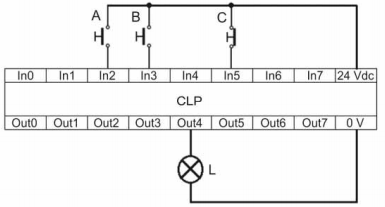

Ainda conforme a figura acima, duas entradas do CLP recebem duas chaves tipo pushbutton NA (A e B), uma terceira entrada

recebe uma chave tipo pushbutton tipo NF (C) e uma saída recebe uma lâmpada que acende em 24V (L), pretende-se

implementar a seguinte lógica:

Ainda conforme a figura acima, duas entradas do CLP recebem duas chaves tipo pushbutton NA (A e B), uma terceira entrada

recebe uma chave tipo pushbutton tipo NF (C) e uma saída recebe uma lâmpada que acende em 24V (L), pretende-se

implementar a seguinte lógica:

− L nunca acende na condição de C fechado. − L deve acender se A ou B estiverem fechadas.

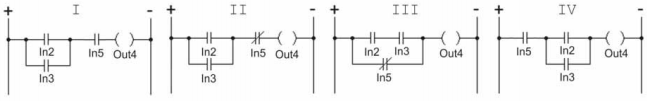

Para isso foram fornecidas as quatro opções de programação em diagrama ladder mostradas abaixo.

Com o exposto acima, é correto afirmar APENAS que: