Questões de Concurso

Foram encontradas 2.168 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

PORT (a, b, c: IN bit;

d, e: OUT bit);

END entidade;

ARCHITECTURE arquitetura OF entidade IS

BEGIN

PROCESS (a, b, c)

BEGIN

IF (c = '1') THEN

d <= a XOR b;

e <= a AND b;

ELSE

d <= '0';

e <= '0';

END PROCESS;

END arquitetura;

Contador Flip-Flop JK

A figura acima mostra um contador binário conectado a um flip-flop JK, ambos com entrada de clock acionada por borda. O contador está programado para decrementar (D/U = 1) e, no início da contagem, Q = Q1 = Q0 = 0, sendo Q1 mais significativo do que Q0. Além disso, cada pulso de clock do contador (Clk1) é seguido por um pulso de clock do flip-flop (Clk2), havendo tempo suficiente para a estabilização das saídas de ambos os dispositivos.

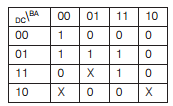

Mapa de Karnaugh de Y

O mapa de Karnaugh mostrado na figura acima representa a seguinte função lógica:

Sobre o resultado a ser encontrado, o resultado esperado (entre parênteses), a correção do programa e a eficácia do teste, pode-se dizer que:

Tais características são alcançadas pelo uso dos seguintes estágios amplificadores em série:

Para que este transistor opere como uma fonte de corrente, é necessário que as seguintes relações sejam satisfeitas:

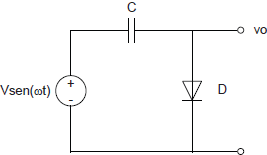

No circuito acima, considere os componentes como sendo ideais. Ao aplicar-se na entrada do circuito um sinal senoidal da forma Vsen(ωt), o sinal de saída vo será, aproximadamente, o de:

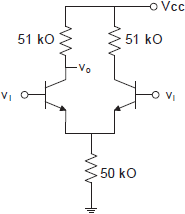

No amplificador diferencial da figura acima, os transistores apresentam fator β igual a 70 e resistência interna de base (rb) igual a 40 kΩ.

O seu ganho de modo comum vo/vi é igual a:

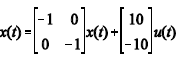

y(t) = [-1 1] x(t)

O diagrama de blocos acima representa a modelagem de uma planta controlada por um controlador do tipo proporcional que apresenta como entrada um sinal de erro obtido a partir da diferença entre o sinal de entrada U(s) e a saída Y(s). A partir dessas informações, julgue o item.

Caso K assuma valor estritamente negativo, o sistema será

instável.

O diagrama de blocos acima representa a modelagem de uma planta controlada por um controlador do tipo proporcional que apresenta como entrada um sinal de erro obtido a partir da diferença entre o sinal de entrada U(s) e a saída Y(s). A partir dessas informações, julgue o item.

Esse sistema, para qualquer valor de K não nulo, nunca terá

zero finito.

Na situação em que K = 0,1, o sistema será subamortecido.

A função de transferência (FT) de um sistema contínuo com resposta impulsional h(t) é dada por  , em que s é uma variável complexa utilizada na definição da transformada de Laplace. A FT do sistema amostrado com período de amostragem T é obtida efetuando-se a transformação do plano s no plano z por meio da expressão z = esT. A transformação efetuada permite a obtenção da transformada z do sistema. Com base nessas informações, julgue o item a seguir.

, em que s é uma variável complexa utilizada na definição da transformada de Laplace. A FT do sistema amostrado com período de amostragem T é obtida efetuando-se a transformação do plano s no plano z por meio da expressão z = esT. A transformação efetuada permite a obtenção da transformada z do sistema. Com base nessas informações, julgue o item a seguir.

No plano z, há, nesse sistema, um polo simples em z = 1.

Com relação à conversão analógica-digital e à digital-analógica, julgue o item a seguir.

Considere um conversor analógico-digital unipolar de 8 bits,

cuja entrada esteja na faixa entre 0 e 12,75 volts, em que a

tensão 0 volt corresponda ao número 00000000, em base 2, e

a tensão 12,75 volts corresponda ao número 11111111. Nessa

situação, caso a tensão de entrada para conversão digital seja

5 volts, o número binário que será apresentado, na saída, após

a conversão, é 11000100.

Considere que a tabela acima apresenta uma tabela verdade que descreve o funcionamento desejado de um circuito digital combinacional com quatro entradas (A, B, C e D) e uma saída (Y).Com relação a essa tabela e a sistemas digitais em geral, julgue o item subsequente.

Caso o circuito apresentado na tabela acima seja implementado com portas TTL padrão, a velocidade de comutação será menor, se comparada à implementação desse circuito com portas CMOS. No entanto, o circuito com portas TTL padrão terá um consumo menor que o circuito com portas CMOS.

Considere que a tabela acima apresenta uma tabela verdade que descreve o funcionamento desejado de um circuito digital combinacional com quatro entradas (A, B, C e D) e uma saída (Y).Com relação a essa tabela e a sistemas digitais em geral, julgue o item subsequente.

A expressão booleana mínima, na forma produto de somas,para a saída Y é dada por Y = (B + D).(A + D)