Questões de Concurso

Foram encontradas 2.169 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

A eficiência espectral de um sistema de transmissão digital que utiliza 256-QAM corresponde a, no máximo, 8 bps/Hz.

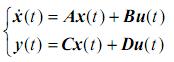

A seguir, é mostrada a representação de um sistema linear contínuo no tempo em que

.

.

Para que o sistema em análise seja observável, a matriz de observabilidade deverá ter posto igual a 3.

A seguir, é mostrada a representação de um sistema linear contínuo no tempo em que

.

.

O sistema em questão possui um autovalor igual a 3.

O módulo da função de transferência G (S) = 1/ S + 2 para 2 rad/s é menor que 1/2.

O ganho DC da função de transferência G(s) é menor que 2.

O sistema representado por G(s) é controlável.

Durante a realização do processo para aquisição de um sinal, a etapa de quantização é seguida pela etapa de amostragem.

Durante a conversão analógica-digital de um sinal, a etapa de codificação tem como propósito representar cada amostra quantizada por meio de uma palavra digital com um número finito de símbolos.

Um sistema cuja resposta ao impulso seja dada pela função h(t) = e-t sen(3t), em que t é uma variável temporal contínua, será instável em regime permanente.

Se um conversor analógico-digital tiver entrada analógica entre 0 V e 5 V e saída de 8 bits que formem números entre 0 e 255, então uma entrada de 2 V corresponderá à saída 102.

Em um conversor digital-analógico que utilize uma rede R-2R, a dependência da precisão do conversor relativamente à precisão dos resistores será muito maior que a de um conversor digital-analógico que utilize uma rede de resistores ponderados em que os valores dos resistores cresçam como uma série geométrica com razão 2.

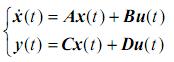

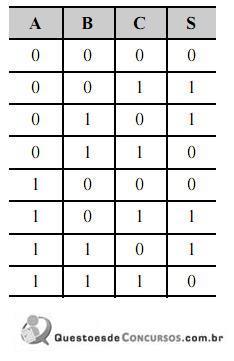

Considerando a tabela-verdade mostrada acima, que descreve o funcionamento de um circuito digital com entradas A, B e C, e saída S, julgue o item seguinte.

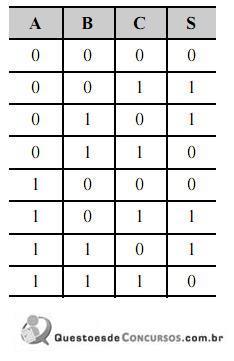

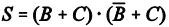

A expressão lógica mínima para a saída S, na forma de produto de somas, é

.

.

Considerando a tabela-verdade mostrada acima, que descreve o funcionamento de um circuito digital com entradas A, B e C, e saída S, julgue o item seguinte.

A expressão lógica mínima para a saída S, na forma de soma de produtos, é

Considerando a tabela-verdade mostrada acima, que descreve o funcionamento de um circuito digital com entradas A, B e C, e saída S, julgue o item seguinte.

Entre todas as famílias lógicas, a família ECL é a que permite implementar o circuito digital relativo à tabela-verdade em apreço com o menor consumo de potência, porém, com menor velocidade de comutação.

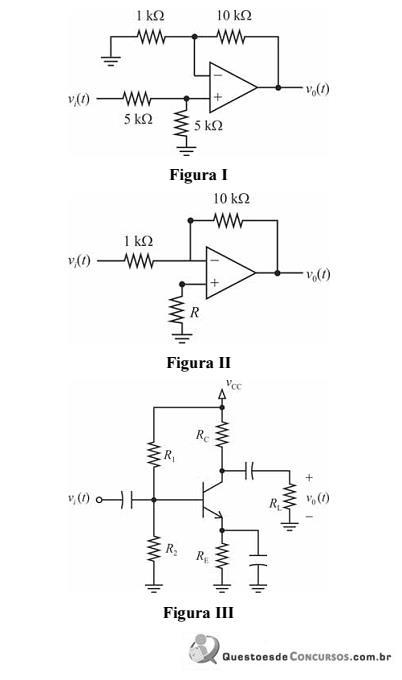

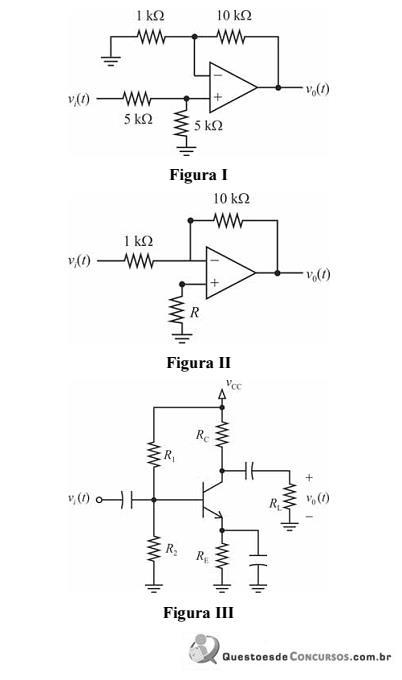

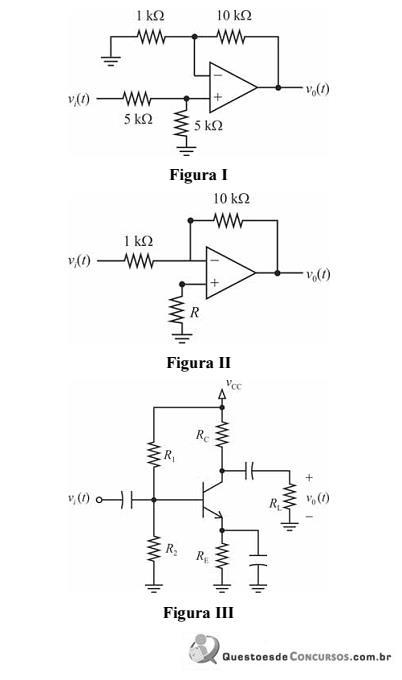

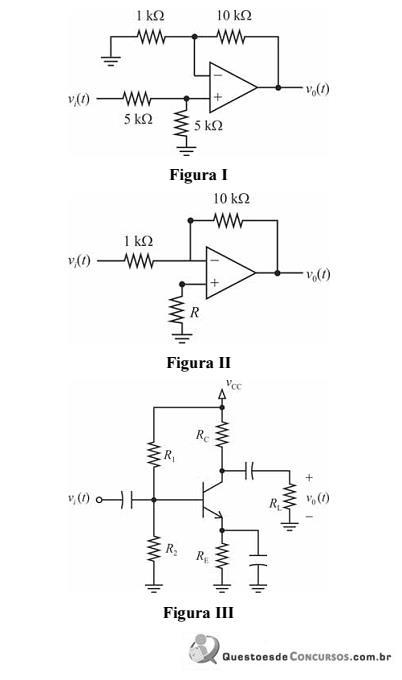

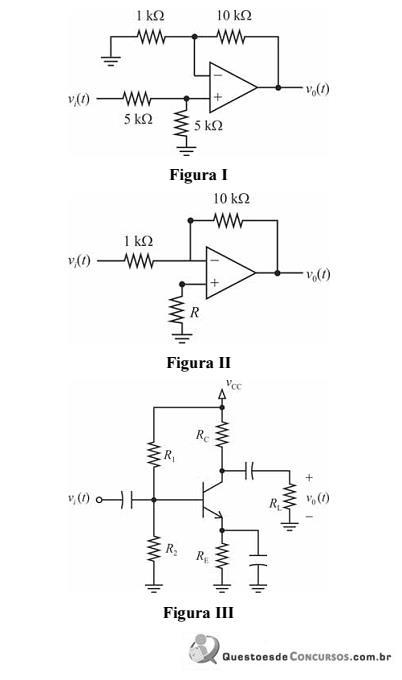

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura I, o ganho de tensão da entrada para a saída é igual a 10.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura III, como o transistor está operando na região ativa, ambas as junções base-emissor e coletor-base estão polarizadas diretamente.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

O amplificador ilustrado na figura III está na configuração coletor comum e possui ganho unitário.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura II, se um capacitor com capacitância de 100 nF for adicionado em paralelo com o resistor de resistência 10 kΩ, então o circuito terá uma resposta em frequência do tipo passa-baixa, cuja frequência de corte é superior a 10 Hz.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

No circuito da figura II, a razão entre a tensão de saída e a de entrada é igual a -10.

As figuras I, II e III acima apresentam circuitos amplificadores, nos quais vi (t) e v0(t) são, respectivamente, os sinais de entrada e de saída. No circuito da figura III, considere que o transistor está polarizado na região ativa e os capacitores são tais que sua impedância é desprezível na faixa de passagem do sinal a ser amplificado. A partir dessas informações, julgue o próximo item.

A impedância de saída do amplificador realimentado mostrado na figura I é igual a 10 kΩ.