Questões de Concurso

Foram encontradas 2.174 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Considere as informações a seguir para responder à questão.

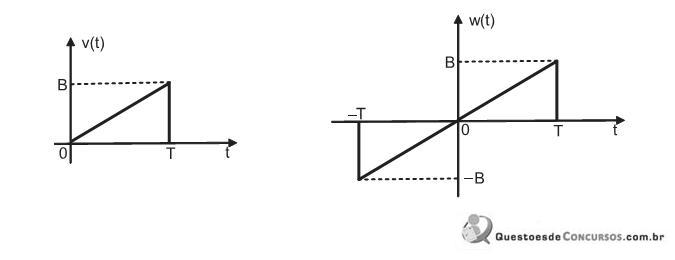

O controle de atitude de um satélite em órbita consiste em ajustar, automaticamente, o ângulo de seu eixo, de modo a direcionar sua antena para a região desejada na superfície da Terra. O modelo simplificado desse sistema consta de um sinal de entrada, que é o torque τ(t), e de um sinal de saída, que é o ângulo θ(t). Considerando o vetor de estado X(t)=  definido com x1(t) =

definido com x1(t) =  (t) , posição angular e x2(t) =

(t) , posição angular e x2(t) =  (t) = dθ / dt , a velocidade angular, obtém-se o seguinte modelo em espaço de estado.

(t) = dθ / dt , a velocidade angular, obtém-se o seguinte modelo em espaço de estado.

e y(t) = [1,0] x(t)

e y(t) = [1,0] x(t)

Aplicando uma realimentação de estado, com a lei de controle dada por τ(t)= - KX(t)= -[k1 k2] X(t), o valor do vetor de ganhos K, que conduz os polos em malha fechada para as posições -2 e -3, é

, onde

, onde •ζ = cos (Φ) é a razão de amortecimento; e

• ωn é a frequência natural não amortecida.

Para discretizar esse sistema e aplicar um controle digital, o período de amostragem deve ser tal que ocorram 10 amostras durante o tempo de subida. O valor aproximado desse período é

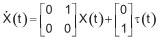

O modelo discreto de um sistema, em malha aberta, é representado pela função de transferência G(z) = K(z +1) / z2 -1,5z + 0,5. A figura acima mostra o esboço do lugar das raízes, no plano Z, para esse sistema, em malha fechada, com realimentação de saída e com o ganho variando no intervalo 0 ≤ k < + ∞ . O circulo unitário está traçado com linha pontilhada. O valor do ganho K, para que o sistema em malha fechada esteja no limiar da instabilidade, é

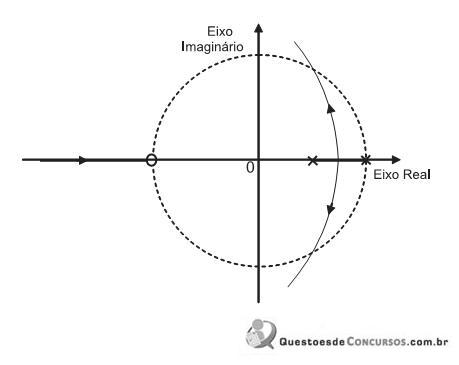

Um sistema discreto de 2ª ordem é composto por dois polos complexos, conjugados, que estão representados no diagrama de polos e zeros da figura acima. O círculo unitário está traçado com linha pontilhada. A resposta ao impulso desse sistema gera um sinal, discreto, senoidal amortecido e que oscila na frequência de 25π rad/s. Nessas condições, o período de amostragem, em ms, usado na discretização desse sistema, é

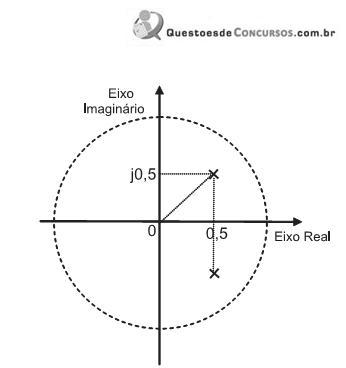

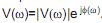

A figura acima mostra dois sinais, na forma de pulsos limitados no tempo. Considere que a transformada de Fourier de v(t) é dada pela expressão, na forma polar,

. Com base nas propriedades da transformada de Fourier e considerando as semelhanças e simetrias entre os dois pulsos, a expressão da transformada de w(t) é

. Com base nas propriedades da transformada de Fourier e considerando as semelhanças e simetrias entre os dois pulsos, a expressão da transformada de w(t) éG(s) = K

s² + as + b

Esse sistema opera com razão de amortecimento 0,7 e frequência natural não amortecida de 15 rad/s. Quando alimentado por um degrau unitário em sua entrada, a saída, em regime permanente, atinge o valor 0,4. Os valores de a e K, respectivamente, são

Os valores de p e z são, respectivamente,

Esse conversor apresenta quatro chaves controláveis (TA+, TA- , TB+ e TB- ) e seus respectivos diodos em antiparalelo (DA+, DA- , DB+ e DB- ). Adicionalmente, o conversor é alimentado por uma tensão CC constante Vd , e vo é a tensão de saída. Nessas condições, o índice de modulação de frequência (mf ) e o índice de modulação de amplitude (ma ) desse conversor são, respectivamente,

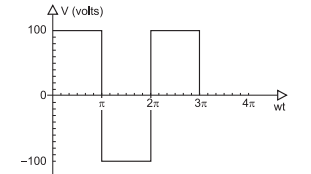

Considere um conversor CA-CC monofásico, de onda completa e retificado a diodo. Esse conversor é alimentado por um outro conversor monofásico CC-CA, cuja tensão de saída é uma onda quadrada, de frequência 60 Hz, mostrada na figura acima. Supondo-se que os dois conversores são considerados ideais, o valor da potência média, em watts, dissipada em uma resistência de 10 Ω conectada no lado CC do retificador, é

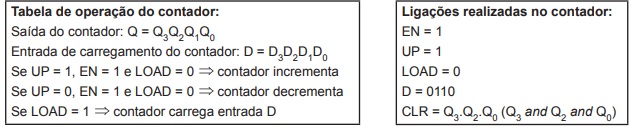

Considere um contador binário de 4 bits, cujas tabelas de operação e de ligações estão mostradas acima. O contador dispõe dos sinais LOAD (carregamento paralelo sincronizado pelo clock), CLR (clear síncrono) e EN (habilitador de contagem a cada clock), todos ativados em nível alto, além do sinal UP, que define a direção de contagem. Sabendo-se que a habilitação de LOAD tem prioridade sobre a habilitação de contagem, o número de estados da sequência permanente implementada é