Questões de Concurso

Foram encontradas 2.186 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Os valores de p e z são, respectivamente,

Esse conversor apresenta quatro chaves controláveis (TA+, TA- , TB+ e TB- ) e seus respectivos diodos em antiparalelo (DA+, DA- , DB+ e DB- ). Adicionalmente, o conversor é alimentado por uma tensão CC constante Vd , e vo é a tensão de saída. Nessas condições, o índice de modulação de frequência (mf ) e o índice de modulação de amplitude (ma ) desse conversor são, respectivamente,

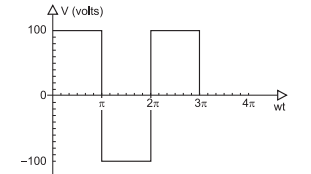

Considere um conversor CA-CC monofásico, de onda completa e retificado a diodo. Esse conversor é alimentado por um outro conversor monofásico CC-CA, cuja tensão de saída é uma onda quadrada, de frequência 60 Hz, mostrada na figura acima. Supondo-se que os dois conversores são considerados ideais, o valor da potência média, em watts, dissipada em uma resistência de 10 Ω conectada no lado CC do retificador, é

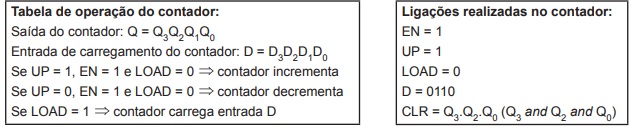

Considere um contador binário de 4 bits, cujas tabelas de operação e de ligações estão mostradas acima. O contador dispõe dos sinais LOAD (carregamento paralelo sincronizado pelo clock), CLR (clear síncrono) e EN (habilitador de contagem a cada clock), todos ativados em nível alto, além do sinal UP, que define a direção de contagem. Sabendo-se que a habilitação de LOAD tem prioridade sobre a habilitação de contagem, o número de estados da sequência permanente implementada é

é

é

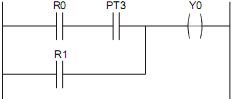

a lógica de programação Ladder correspondente é

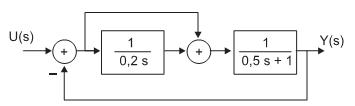

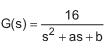

O diagrama em blocos da figura acima mostra um sistema linear com entrada U(s) e saída Y(s). Com base nos dados do diagrama, os polos desse sistema em malha fechada são

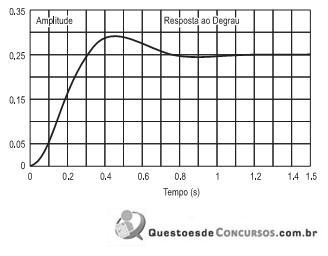

O gráfico da figura acima corresponde à resposta ao degrau unitário de um sistema de 2ª ordem, cuja função de transferência é

. Com base nos dados da figura, o valor da Frequência Natural Não Amortecida é

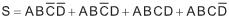

. Com base nos dados da figura, o valor da Frequência Natural Não Amortecida é , a lógica de programação Ladder correspondente é

, a lógica de programação Ladder correspondente é

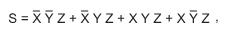

A expressão lógica que o representa é: