Questões Militares de Engenharia Eletrônica - Álgebra Booleana e Circuitos Lógicos em Engenharia Eletrônica

Foram encontradas 139 questões

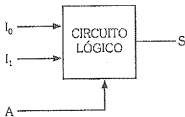

Analise a figura a seguir.

Considerando que, em função do nível lógico aplicado a uma

entrada de seleção A, o circuito combinacional acima deve

comutar à saída os sinais aplicados nas entradas digitais

conforme a seguinte convenção: A = 0 => a entrada digital I0

é comutada para saída S ; A = 1 => a entrada digital I1 é

comutada para saída S . Sendo assim, assinale a opção que

apresenta a expressão booleana que representa esse circuito,

sabendo que ele funciona como uma chave seletora digital com

2 entradas e 1 saída digital.

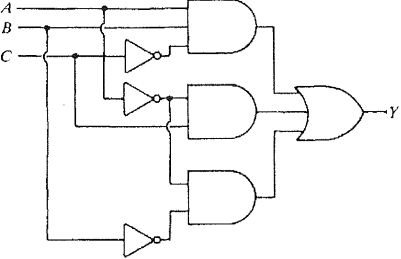

Analise a figura a seguir.

Assinale a opção que corresponda à expressão da saída Y do

circuito lógico do diagrama acima.

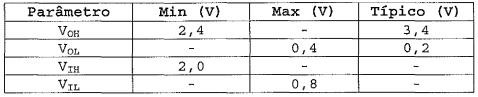

Analise a tabela a seguir.

As especificações das tensões de entrada e saída para a

família TTL padrão estão relacionadas na tabela acima. De

acordo com essas informações, determine a maior amplitude do

ruído que poderá ser tolerada quando uma saída de nível lógico

alto estiver acionando uma entrada, e assinale a opção

correta.

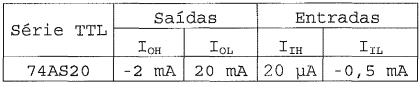

Considere os parâmetros de corrente da Série de Circuitos Integrados (Cl) TTL 74AS20 conforme a tabela abaixo.

Onde :

I0H = Corrente de Saída em Nível Alto

I0L - Corrente de Saída em Nível Baixo

IIH = Corrente de Entrada em Nível Alto

IIL - Corrente de Entrada em Nível Baixo

Com base na tabela acima assinale a opção que apresenta o

número de portas de entrada que um Cl 74AS20 pode acionar de

outro Cl 74AS20.

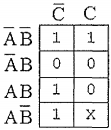

Analise a figura a seguir.

Determine a expressão lógica simplificada para o mapa de

Karnault apresentado acima e assinale a opção correta.