Questões Militares

Sobre flip-flops em engenharia eletrônica

Foram encontradas 38 questões

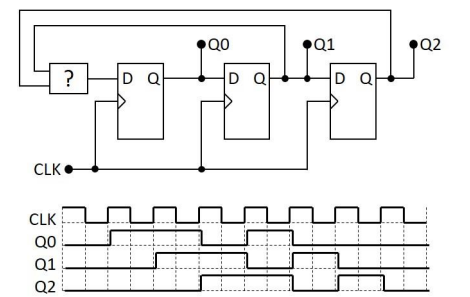

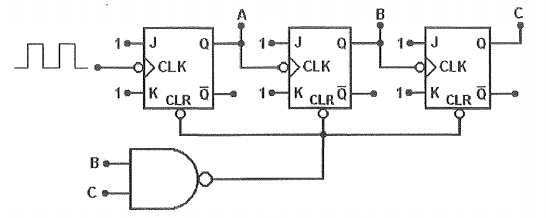

O circuito cujo diagrama esquemático abaixo apresenta um circuito composto por três flip-flops e uma porta lógica desconhecida.

Para que o circuito funcione conforme o diagrama temporal acima, o bloco marcado com uma interrogação deve ser

substituído por uma porta:

Os parâmetros que devem ser considerados para o perfeito funcionamento do Flip Flop estão corretamente indicados em

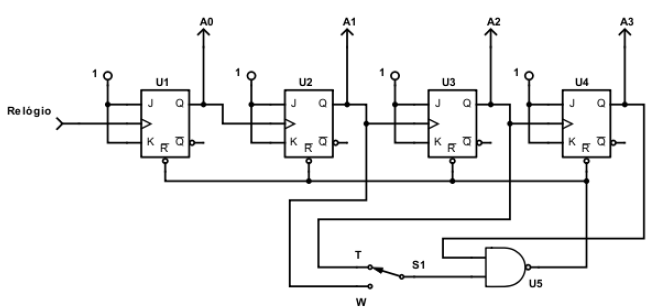

Abaixo temos um contador digital implementado com 4 (quatro) flip-flops tipo JK.

Informe se é verdadeiro (V) ou falso (F) o que se afirma abaixo sobre o contador digital.

( ) É um contador modo 16. ( ) Quando a chave S1 está no posição T (tal como na figura), é um contador modo 13. ( ) Quando a chave S1 está no posição W (posição outra do que a da figura) é um contador modo 10. ( ) Além dos estados firmes que definem o modo do contador, esse contador apesenta um estado de transição.

Marque a alternativa com a sequência correta.

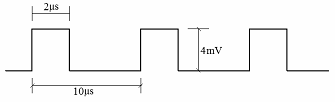

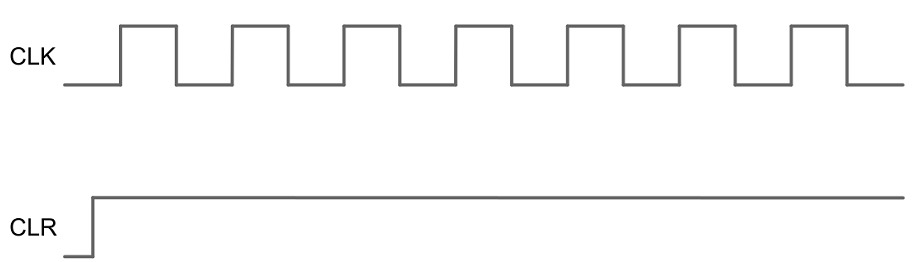

Observe o trem de pulsos ilustrado abaixo em que amplitude, duração e período são constantes. Qual o ciclo de trabalho desse trem de pulsos?

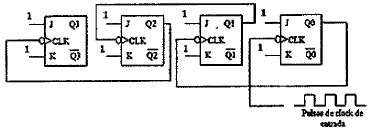

Analise o circuito a seguir.

Considere que todas as entradas J e K dos Flip-Flops estão em nível lógico alto. Em relação ao circuito acima, qual será a frequência na saída do último Flip-Flop (Q3), quando a frequência do clock de entrada for de 1MHz?

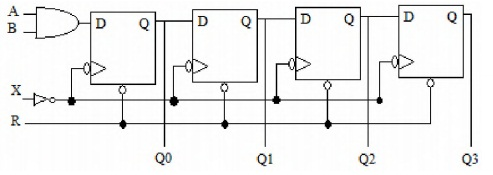

Julgue os itens a seguir em V (verdadeiro) ou F (falso) e assinale

a alternativa com a sequência correta. ( ) é um circuito de entrada serial e saída paralela.

( ) as saídas são atualizadas a cada borda de descida de X.

( ) quando R=1, todas as saídas apresentam nível lógico zero.

Julgue os itens a seguir em V (verdadeiro) ou F (falso) e assinale

a alternativa com a sequência correta. ( ) é um circuito de entrada serial e saída paralela.

( ) as saídas são atualizadas a cada borda de descida de X.

( ) quando R=1, todas as saídas apresentam nível lógico zero.Admitindo-se que as entradas dos flip-flops J-K estejam em nível alto, e Q representa a saída, assinale a opção que apresenta o tipo de contador da figura.

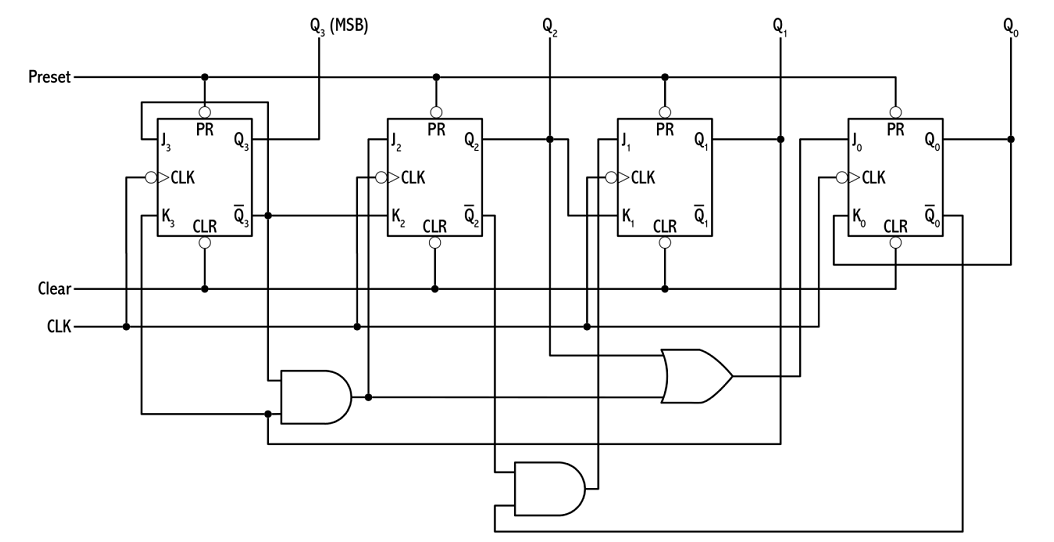

A figura abaixo mostra um contador síncrono de 4 bits implementado a partir de flip-flops JK, onde Q3, Q2, Q1 e Q0 são as saídas binárias de cada flip-flop e o Q3 é o bit mais significativo (Most Signficant Bit – MSB) desse contador.

Para o circuito acima as entradas Presets (PR) estão em nível alto o tempo todo e os valores iniciais das entradas Clock (CLK) e Clear são mostrados na figura abaixo. Enquanto o circuito desse contador permanecer ligado e após o período inicial de tempo mostrado na figura abaixo, o CLK continuará alternando entre os níveis baixo e alto e CLR=1.

A sequência numérica, na base decimal, da saída desse contador síncrono é representada por:

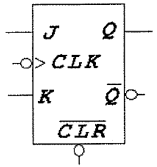

Observe o diagrama esquemático do Flip-Flop do tipo JK apresentado pela figura abaixo.

Com base na análise do componente apresentado, qual o procedimento que deve ser realizado para transformar

um Flip-Flop JK em um Flip-Flop tipo D?

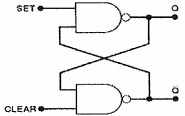

Assinale a opção que identifica corretamente o dispositivo cujo diagrama lógico foi representado na figura acima.

l. Flip-flop JK: sua saída é chaveada quando as entradas J = K = 1.

ll. Flip-flop D: utiliza um flip-flop tipo JK, porém, com as entradas conectadas juntas, resultando numa única entrada, denominada entrada D.

lll. Flip-flop T: utiliza um flip-flop tipo JK com as entradas J e K conectadas a um inversor, de forma que quando J = 1, K = 0 e vice-versa, resultando numa única entrada, denominada de entrada T.

lV. Flip-flop RS: este tipo é o mais simples, base para outros tipos como o JK.

Estão corretas somente as afirmativas

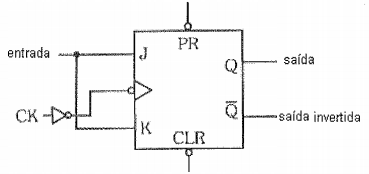

Analise a figura a seguir.

Qual é o tipo de Flip-Flop representado na figura acima?