Questões de Concurso Militar EEAR 2021 para Eletrônica

Foram encontradas 100 questões

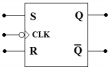

Avalie as informações abaixo com relação ao flip-flop RS ilustrado.

I - O clock é ativado na transição do nível lógico 1 para 0 devido à

presença da inversora.

II - A saída Q não sofre alteração de estado lógico quando as entradas R e S estão em nível lógico 0, independente das transições do clock.

III - O clock tem a função de habilitar as mudanças de estado de saída Q em função das entradas R e S, e esta habilitação ocorre quando o clock mantém-se no nível lógico 0.

IV - As saídas Q e “Q barrado” podem ter o mesmo nível lógico (0 ou 1). Essa condição é obtida pela presença da inversora na entrada de clock com nível lógico 1 aplicado.

Está correto o que se afirma em

( ) A principal desvantagem de um CI construído com tecnologia MOS é sua alta sensibilidade à eletricidade estática que pode danificá-lo com relativa facilidade.

( ) Um CI com tecnologia MOS foi projetado para ser compatível com todos os seus correspondentes TTL, porém com maior capacidade de integração e menor consumo de potência.

( ) A série 74 de CIs digitais representa CIs fabricados com tecnologia TTL, tais como 74LS, 74AS, 74HC, 74HCT, etc., em que a diferença entre eles está na diferença entre parâmetros elétricos.

( ) CMOS é a tecnologia MOS na qual há a utilização, em um mesmo circuito digital (por exemplo, um inversor), de MOSFETs canal N e canal P.