Questões Militares Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 139 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

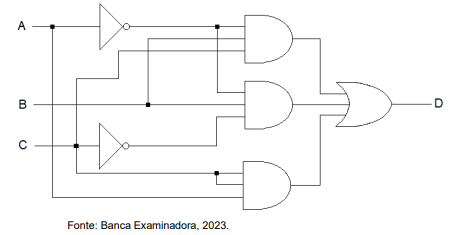

O diagrama mostrado na figura abaixo representa parte de um sistema digital implementando uma função booleana com portas lógicas.

Considerando as informações e o diagrama da figura acima, qual é a expressão para a saída D?

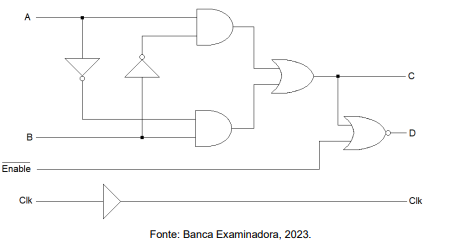

Com base na figura e informações acima, a função lógica disponibilizada na saída C é do tipo

A forma de onda que corresponde corretamente à saída X do circuito mostrado é:

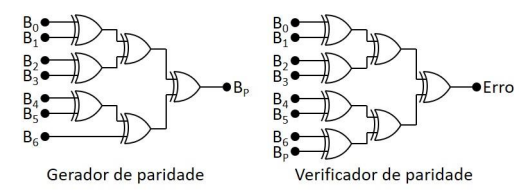

2O projetista de uma empresa foi encarregado de projetar um circuito gerador de paridade par para uma palavra de sete bits. Um outro projetista foi encarregado de projetar um circuito verificador de paridade para trabalhar com dados com paridade ímpar e que deve gerar um sinal de erro com nível lógico alto se houver erro em um dos bits recebidos.

Analise abaixo os diagramas esquemáticos dos dois circuitos projetados.

Sobre os circuitos acima, e considerando-se as especificações de cada um, é correto afirmar que:

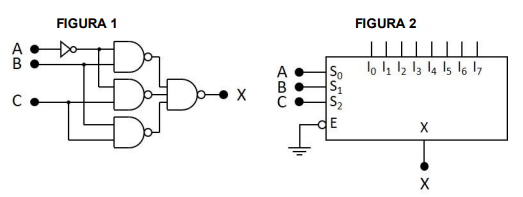

Analise abaixo os diagramas esquemáticos de dois circuitos, sendo o que primeiro emprega portas lógicas e o segundo, um multiplexador com oito entradas, onde I0 a I7 são as entradas de dados, S0 a S2 são as entradas de seleção, sendo S2 a mais significativa e E é uma entrada de habilitação ativa em nível lógico baixo.

As entradas do multiplexador podem ser ligadas ao nível lógico baixo (0) ou nível lógico alto (1). Para que o circuito

com o multiplexador seja funcionalmente equivalente ao circuito com portas lógicas, ou seja, para que a cada uma

das possíveis combinações das entradas ambos os circuitos tenham saídas iguais, as entradas do multiplexador I0 a

I7 deverão ser ligadas, respectivamente, a: