Questões Militares

Para engenharia eletrônica

Foram encontradas 1.006 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

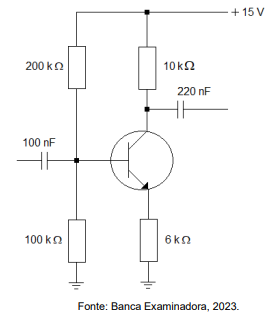

O estágio amplificador mostrado na figura abaixo usa um transistor operando com β = 100 e Vbe = 0,7 V.

Considerando as informações e estágio amplificador da figura acima, o valor da corrente de coletor em estado

quiescente é:

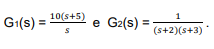

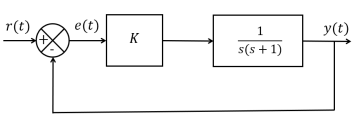

Considere para o sistema de controle mostrado abaixo,

Qual é a função de transferência do sistema?

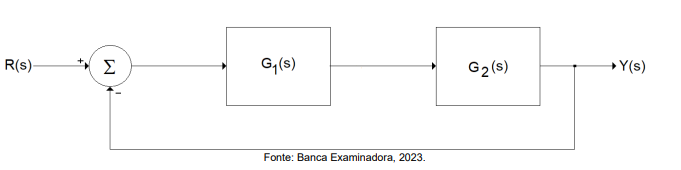

Com base no sistema da figura acima, usando componentes ideiais, a expressão de Vo como uma função de Vs é

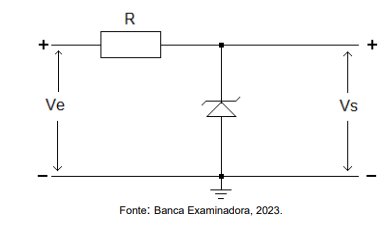

Diodo Zener: 1N4733A

Vzener = 5,1 V ± 5%, e Rdinâmica = 7 Ω para Izener = 50 mA

PD = 1 W

Com base nas informações e no circuito da figura acima, o valor do resistor R para corrente máxima no diodo de 50 mA e a regulação da tensão de saída Vs em valor percentual, ao longo da faixa de tensão de entrada, devem ser, respectivamente

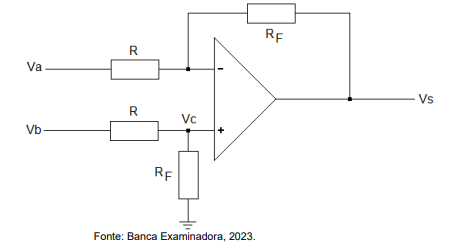

O circuito abaixo usa um amplificador operacional ideal, onde RF = 2R.

Com base nas informações e no circuito da figura acima, sendo Va = 8 V e Vb = 9 V, as amplitudes do sinal de saída

Vs e do sinal em Vc são, respectivamente

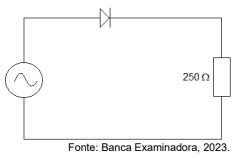

Com base nas informações e no circuito da figura acima, a tensão eficaz que deve ser fornecida pela fonte é

Ao se aplicar um sinal r(t) do tipo degrau com amplitude finita, é esperado que o valor do sinal de erro e(t), em regime permanente, convirja para:

G(S) = 10/s+20

é submetido à uma entrada tipo degrau unitário. O valor da resposta forçada desse sistema e o tempo necessário para atingir 98% do valor final são, respectivamente:

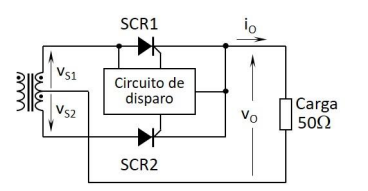

O primário do transformador do circuito, cujo diagrama esquemático abaixo, está ligado a um barramento CA com tensão eficaz de 220 V e frequência de 60 Hz. A relação de espiras do transformador e o ângulo de disparo dos SCRs foram ajustados de tal maneira que, para todos os componentes funcionando corretamente, o valor eficaz da tensão de saída (VO) seja igual a 100 V. Entretanto, o SCR1 desse circuito apresentou um defeito, passando a se comportar permanentemente como um circuito aberto.

Na situação de defeito apresentada, qual é o valor eficaz da tensão de saída?

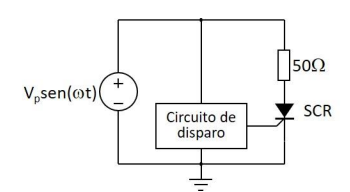

Abaixo é apresentado o diagrama esquemático de um circuito, onde o SCR recebe um pulso de disparo no ângulo ωt = 90º (o mesmo que π/2 radianos). O circuito recebe em sua entrada uma tensão com forma de onda senoidal cujo valor de pico VP = 100π V.

O valor médio da corrente no resistor é igual a:

Uma determinada memória RAM trabalha com uma palavra de dados de 8 bits e tem um sistema de endereçamento multiplexado em duas etapas, controlado por dois sinais, RAS e CAS. Inicialmente, o barramento de endereço dessa memória recebe 5 bits de endereço de linha e o sinal RAS é pulsado. Depois, o barramento de endereço recebe 6 bits de endereço de coluna e o sinal CAS é pulsado.

Qual é a capacidade dessa memória em bytes?

Analise as afirmativas abaixo quanto aos dispositivos lógicos programáveis (PLD):

I. Um PLD do tipo arranjo lógico programável (PLA) tem um arranjo de portas AND/OR e são programáveis com a queima de fusíveis em uma matriz, com a vantagem de serem totalmente reprogramáveis.

II. Os dispositivos lógicos programáveis complexos (CPLD) que empregam tecnologia de programação EEPROM são apagáveis, reprogramáveis e não voláteis.

III. PLDs do tipo matrizes de portas programáveis em campo (FPGA) podem utilizar uma tabela de consulta (LUT) para criar as funções combinacionais desejadas, sendo que uma LUT de N entradas funciona como uma tabela-verdade para 2N-1 combinações possíveis.

IV. Os FPGAs baseados em SRAM necessitam, para a sua configuração, de uma memória externa cujo conteúdo é transferido para o FPGA quando o dispositivo é energizado.

V. Uma diferença entre CPLD e FPGA é que, no primeiro, os recursos internos de roteamento de sinal lógico programável tendem a ser uniformes em todo o chip, produzindo atrasos de sinal consistentes, enquanto que, no segundo, tendem a ser bem variados, com extensões de caminhos diferentes disponíveis e, portanto, atrasos diferentes.

Sobre as afirmativas acima, é correto afirmar que:

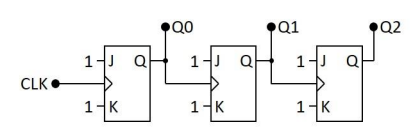

Sabendo-se que, em um determinado instante, o valor binário das saídas Q2Q1Q0, tomadas nessa ordem, é igual a 010, qual o valor binário das saídas após 5 ms?

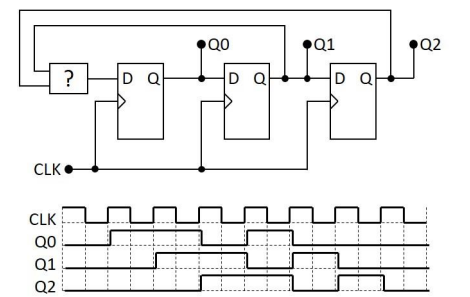

O circuito cujo diagrama esquemático abaixo apresenta um circuito composto por três flip-flops e uma porta lógica desconhecida.

Para que o circuito funcione conforme o diagrama temporal acima, o bloco marcado com uma interrogação deve ser

substituído por uma porta:

A forma de onda que corresponde corretamente à saída X do circuito mostrado é:

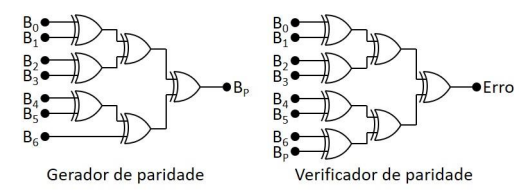

2O projetista de uma empresa foi encarregado de projetar um circuito gerador de paridade par para uma palavra de sete bits. Um outro projetista foi encarregado de projetar um circuito verificador de paridade para trabalhar com dados com paridade ímpar e que deve gerar um sinal de erro com nível lógico alto se houver erro em um dos bits recebidos.

Analise abaixo os diagramas esquemáticos dos dois circuitos projetados.

Sobre os circuitos acima, e considerando-se as especificações de cada um, é correto afirmar que:

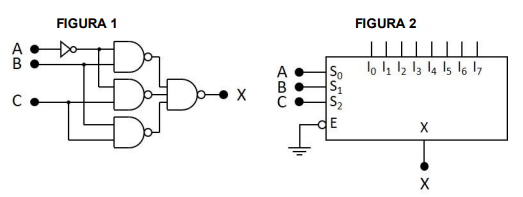

Analise abaixo os diagramas esquemáticos de dois circuitos, sendo o que primeiro emprega portas lógicas e o segundo, um multiplexador com oito entradas, onde I0 a I7 são as entradas de dados, S0 a S2 são as entradas de seleção, sendo S2 a mais significativa e E é uma entrada de habilitação ativa em nível lógico baixo.

As entradas do multiplexador podem ser ligadas ao nível lógico baixo (0) ou nível lógico alto (1). Para que o circuito

com o multiplexador seja funcionalmente equivalente ao circuito com portas lógicas, ou seja, para que a cada uma

das possíveis combinações das entradas ambos os circuitos tenham saídas iguais, as entradas do multiplexador I0 a

I7 deverão ser ligadas, respectivamente, a:

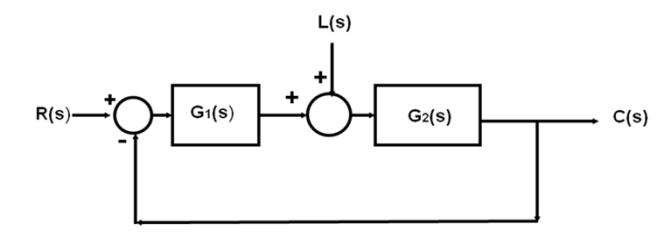

Considere o sistema de controle representado pelo diagrama em blocos abaixo, sendo C(s) a saída do sistema, R(s) o valor do set-point e L(s) o distúrbio.

Pode-se afirmar que, para o sistema de controle regulatório, sendo R(s) = 0, a função de transferência do sistema

será dada por:

Ao aplicar-se uma função de grau r(t) com amplitude 5 à entrada de um sistema de controle por realimentação negativa, representado pela função de transferência Gp(s), obtem-se a resposta temporal: c(t) = 3∙t.

Considere:

Em relação à estabilidade do sistema de controle, é correto afirmar que:

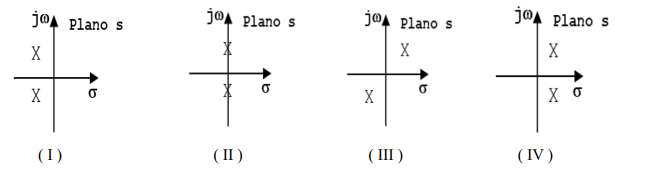

A estabilidade de um amplificador ou outro sistema é determinada diretamente por seus polos.

Analise abaixo os quatro planos s onde os X mostram as diferentes posições dos polos.

O plano s que mostra os polos localizados na posição em que uma excitação por um impulso unitário na entrada

gera, como resposta, uma oscilação sustentável é indicado em: