Questões de Concurso

Sobre circuitos lógicos e álgebra booleana em eletrônica em eletrônica

Foram encontradas 170 questões

Dentre as alternativas a seguir, o circuito mais adequado para fazer a interface entre o dispositivo de controle digital e o driver de motor é:

• Tensão de saída em nível lógico baixo: VOL = 0V

• Tensão de saída em nível lógico alto: VOH = +5V

• Capacidade de corrente de saída em nível lógico baixo: IOL = 10mA

• Capacidade de corrente de saída em nível lógico alto IOH: = -10mA

Esse dispositivo digital deve acionar um motor de corrente contínua (MCC) de tensão e potência nominais 30Vcc/100W, em uma única direção. Para que isso aconteça, o circuito mais adequado é:

A saída D2 representa o bit mais significativo, e D0, o bit menos significativo. Em t=0 segundos, os flip-flops FF0, FF1 e FF2 apresentam nível lógico zero em suas saídas Q.

Com base nessas informações, assinale a alternativa INCORRETA:

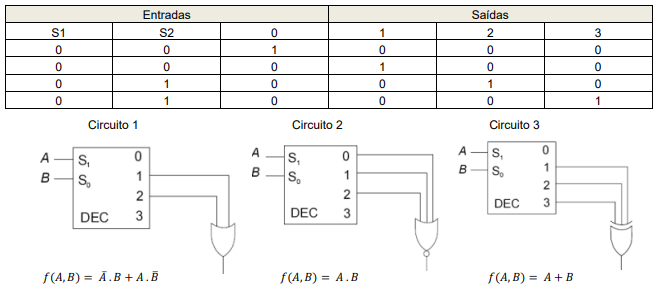

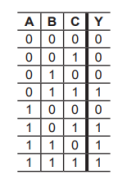

Esse circuito realiza uma função lógica booleana. Uma expressão que descreve essa função é:

Considere o circuito lógico combinacional e sua respectiva Tabela-Verdade, mostrado na figura a seguir.

A função FX corresponde a uma porta lógica do tipo:

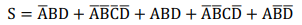

Nessa situação hipotética, a função lógica mínima para a referida função é

Observe a figura a seguir.

Elaborado pelo(a) autor(a).

O tipo de porta lógica para o qual o circuito representado na

figura acima pode ser simplificado é

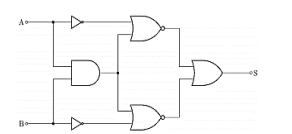

Um determinado processo industrial é representado pela tabela verdade a seguir, composta por três entradas (A, B e C) e uma saída (Y).

Elaborado pelo(a) autor(a).

Qual a opção simplificada da expressão que realiza a tabela

apresentada?

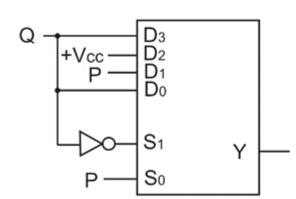

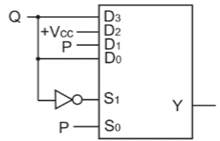

A lógica da saída Y do multiplexador do circuito acima é

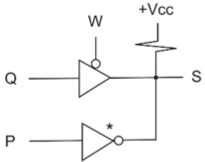

O circuito a seguir é composto por um buffer tri-state, um inversor com saída em coletor aberto e um resistor.

A combinação de sinais que gera conflito em S é

A lógica da saída Y do multiplexador do circuito acima é

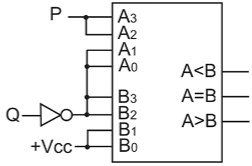

As lógicas das saídas A<B e A=B do comparador unsigned do circuito acima são, respectivamente,

I Contadores assíncronos são caracterizados por seus flip-flops funcionarem de maneira tal que não há entradas de clock em comum.

II Um flip-flop do tipo T é obtido a partir de um flip-flop JK com as entradas J e K curto-circuitadas.

III Em um registrador de deslocamento com flip-flops JK em série, as saídas de cada bloco são aplicadas nas entradas J e K respectivas do flip-flop seguinte.

Assinale a opção correta.

Acerca de contadores em circuitos lógicos, assinale a opção correta.