Questões de Concurso

Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 500 questões

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

Ainda que as famílias apresentadas sejam todas TTL, os

requisitos de interface, corrente e tensão variam de acordo com

a família utilizada.

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

Entre as famílias da tabela, a 74AS possui o pior desempenho

quanto à velocidade, pois é a que tem o menor produto

velocidade-potência.

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

A família 74LS tolera um spike de ruído negativo para o estado

alto de 0,3 V.

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

Entre as famílias apresentadas, a 74 possui maior capacidade

de acionamento de entradas de mesma série.

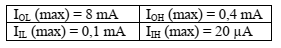

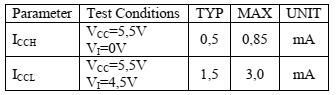

Considerando os dados de especificação técnica da porta NAND 74ALS00, assinale a opção que representa a quantidade de portas que podem ser acionadas em sua saída.

De acordo com as especificações técnicas para o CI 74ALS00, um circuito integrado quádruplo de portas NAND de duas entradas, assinale a alternativa que representa a potência de dissipação térmica média máxima para uma única porta.

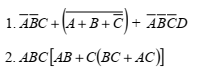

Para implementar a expressão lógica,

, utiliza-se uma porta OR e

, utiliza-se uma porta OR e

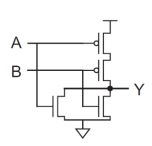

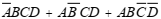

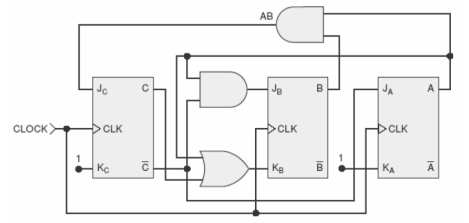

Assinale a alternativa que indica a função lógica realizada pelo circuito da figura abaixo:

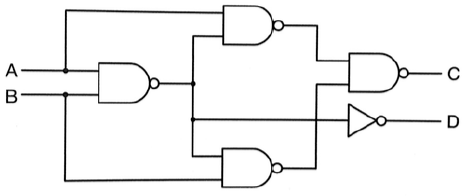

Considere o circuito digital abaixo.

É correto afirmar que

A expressão abaixo foi obtida a partir da simplificação de um circuito lógico.

z = (X̅ + Y)(X + Y + B)B̅

A expressão booleana simplificada para essa expressão é

Os dados transmitidos em um sistema digital podem ser verificados pelo uso de bite de paridade. Considerando o circuito verificador de paridade par mostrado na figura precedente, julgue o item que se segue.

Quando o identificador de paridade identificar um erro,

sua saída irá para o nível alto.

Os dados transmitidos em um sistema digital podem ser verificados pelo uso de bite de paridade. Considerando o circuito verificador de paridade par mostrado na figura precedente, julgue o item que se segue.

Se dois bites forem invertidos, a saída do verificador de

paridade não indicará qualquer erro.

Os dados transmitidos em um sistema digital podem ser verificados pelo uso de bite de paridade. Considerando o circuito verificador de paridade par mostrado na figura precedente, julgue o item que se segue.

Em caso de erro, o verificador de paridade apresentado

não conseguirá identificar qual bite estará errado.

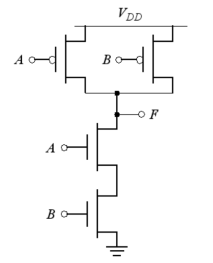

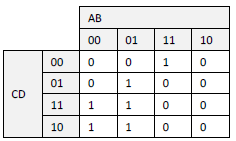

A expressão simplificada do mapa de Veitch Karnaugh, mostrado acima, é

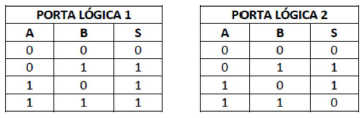

A figura a seguir apresenta a tabela verdade de duas portas lógicas.