Questões de Concurso

Sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 894 questões

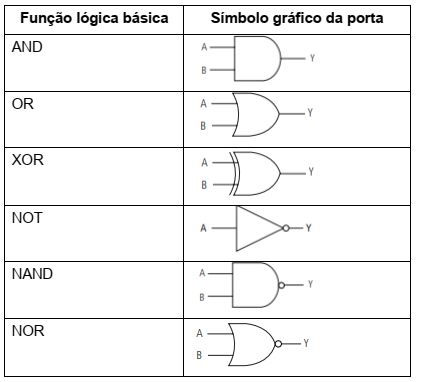

Na eletrônica digital, os sistemas (computadores, processadores de dados, sistemas de controle, codificadores, decodificadores, entre outros) empregam um pequeno grupo de circuitos lógicos básicos, que são conhecidos como portas.

Segundo Monteiro (2007), o projeto de circuitos digitais e a análise de seu comportamento em um computador podem ser realizados por meio da aplicação de conceitos e regras estabelecidas por uma disciplina conhecida como Álgebra de Chaveamentos, a qual é um ramo da Álgebra de Boole ou Álgebra Booleana.

MONTEIRO, M. Introdução à organização de computadores. 5. ed. Rio de Janeiro: LTC, 2007.

A tabela a seguir mostra o resumo dos símbolos gráficos e matemáticos (equação booleana) de portas lógicas.

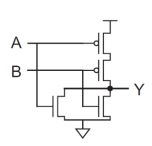

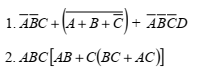

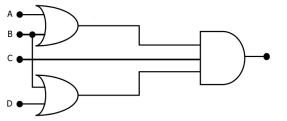

Dado o circuito:

A expressão correta é

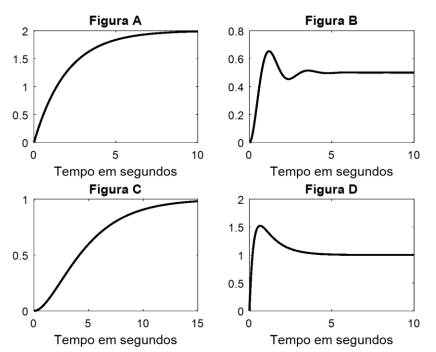

Abaixo a resposta ao degrau unitário de quatro sistemas diferentes.

Analise as afirmativas a seguir:

1. O sistema da figura D possui zero e não é oscilatório.

2. As figuras B e D mostram sistemas oscilatórios e D apresenta o maior sobre-sinal.

3. O sistema da figura A é de 1ª ordem e a constante de tempo é aproximadamente 1,26 segundos.

4. O sistema da figura C têm pelo menos dois polos reais.

5. Os sistemas das figuras B e D têm polos complexos conjugados.

São CORRETAS as afirmativas:

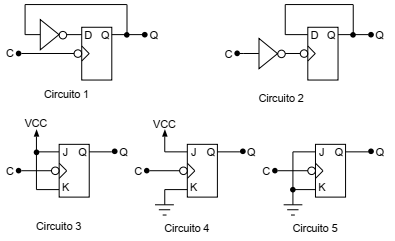

Em relação aos circuitos com flip-flops abaixo, podemos afirmar que o Circuito 1 é funcionalmente equivalente ao:

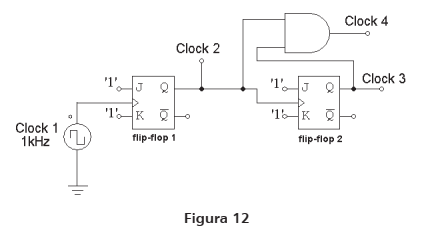

O circuito digital da Figura 12 abaixo utiliza flip-flops do tipo JK, sensíveis à borda de subida do clock. As estradas J e K de ambos os flip-flops foram fixadas em nível lógico alto, conforme mostrado na figura.

O flip-flop 1 está sendo alimentado por um sinal de clock, denominado Clock 1, o qual possui frequência de 1kHz. Os demais

sinais de clock, produzidos pelo circuito, chamados Clock 2, Clock

3 e Clock 4 possuem, respectivamente, frequências iguais a

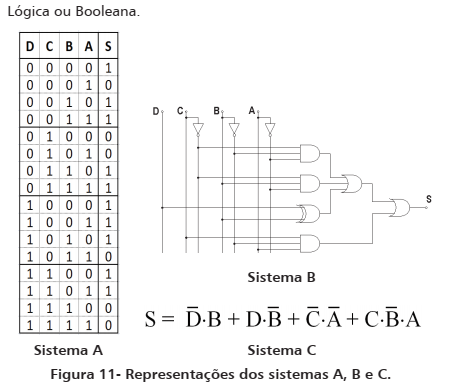

Três diferentes sistemas digitais do tipo Combinacional, A, B e C

são representados na Figura 11 abaixo, sendo o sistema A representado pela sua Tabela Verdade, o Sistema B, pelo seu Diagrama

de Blocos ou Circuito Lógico, e o Sistema C, pela sua Equação

Lógica ou Booleana.

Diferentes sistemas digitais do tipo combinacional são ditos equivalentes se e somente se os valores de suas respectivas saídas forem iguais para cada uma das possíveis combinações de suas variáveis de entrada.

Considerando-se tal conceito de equivalência, é correto afirmar,

em relação aos três sistemas combinacionais A, B e C representados na figura, que

De acordo com a topologia apresentada no circuito da figura anterior, utilizado para realizar uma operação lógica, julgue o próximo item.

Se A = 1 e B = 0, somente os transistores NMOS da entrada

A e os PMOS da entrada B estarão conduzindo.

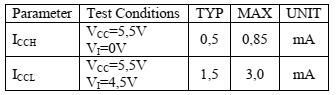

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

Ainda que as famílias apresentadas sejam todas TTL, os

requisitos de interface, corrente e tensão variam de acordo com

a família utilizada.

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

Entre as famílias da tabela, a 74AS possui o pior desempenho

quanto à velocidade, pois é a que tem o menor produto

velocidade-potência.

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

A família 74LS tolera um spike de ruído negativo para o estado

alto de 0,3 V.

Tendo como base a tabela precedente, que apresenta parâmetros para famílias de circuitos lógicos, julgue o item subsecutivo.

Entre as famílias apresentadas, a 74 possui maior capacidade

de acionamento de entradas de mesma série.

Julgue o item que se segue, a respeito do conversor analógico-digital (A/D), considerando a complexidade dos circuitos e a influência da variação de temperatura.

Um conversor do tipo rampa simples possui uma menor

dependência do valor convertido, em relação às variações de

temperatura, se comparado ao conversor de integração por

dupla rampa.

Julgue o item que se segue, a respeito do conversor analógico-digital (A/D), considerando a complexidade dos circuitos e a influência da variação de temperatura.

O conversor por aproximação sucessiva possui um integrador

digital, que aumenta a complexidade do circuito, mas com

ganho em relação à sua robustez.

Julgue o item que se segue, a respeito do conversor analógico-digital (A/D), considerando a complexidade dos circuitos e a influência da variação de temperatura.

Uma das desvantagens do conversor flash é o alto custo de

implantação devido ao tamanho e à complexidade de seus

circuitos.

Julgue o item que se segue, a respeito do conversor analógico-digital (A/D), considerando a complexidade dos circuitos e a influência da variação de temperatura.

Os resistores de peso binário são utilizados na construção de

conversores A/D com baixa dependência à temperatura e com

alta resolução.

No que se refere à eletrônica digital, julgue o item subsequente.

A multiplexação é utilizada para dividir um meio de saída

entre mais de uma entrada. Com um multiplexador digital de quatro entradas, por exemplo, para selecionar a entrada que deverá usar a saída, será necessário utilizar uma equação com um seletor S de entrada com um total de três bits.

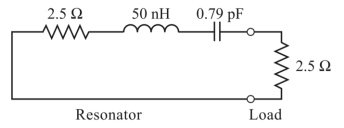

De acordo com o ressonador série RLC da figura abaixo, assinale a alternativa que representa a frequência ressonante do circuito.

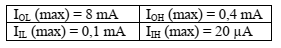

Considerando os dados de especificação técnica da porta NAND 74ALS00, assinale a opção que representa a quantidade de portas que podem ser acionadas em sua saída.

De acordo com as especificações técnicas para o CI 74ALS00, um circuito integrado quádruplo de portas NAND de duas entradas, assinale a alternativa que representa a potência de dissipação térmica média máxima para uma única porta.