Questões de Concurso

Sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 894 questões

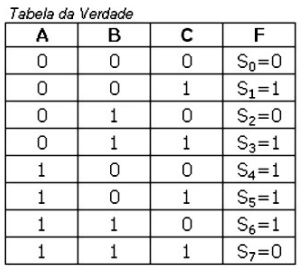

Uma simplificação da expressão booleana

A̅ B̅ C̅ + A̅ B C̅ + A B̅ C̅ D̅ + B̅ C D̅

é:

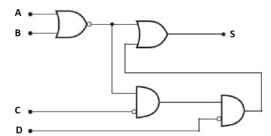

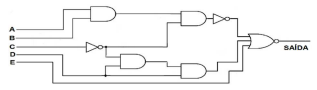

Assinale a opção em que é apresentada a expressão booleana (função lógica) correspondente ao circuito combinacional representado na figura precedente.

Sejam A e B números de 8 bits. Sejam P e Q os

complementos de A e B, respectivamente (ou seja,

P = Ā e Q =  ). Um circuito utiliza dois somadores de

8 bits. No primeiro, são colocados nas entradas os

números P e Q. No segundo, são colocados nas entradas o complemento da saída do primeiro somador e o

número B.

). Um circuito utiliza dois somadores de

8 bits. No primeiro, são colocados nas entradas os

números P e Q. No segundo, são colocados nas entradas o complemento da saída do primeiro somador e o

número B.

Sendo assim, verifica-se que a saída do segundo somador é

Sem levar em conta os inversores, o produto de somas

minimizado da função desenhada no mapa acima é implementado com:

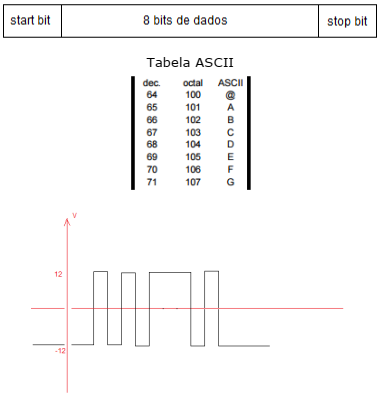

Um sistema eletrônico realiza comunicação serial assíncrona pela interface serial de um computador. Sabendo que os dispositivos enviam os dados com um start bit, 8 bits de dados e um stop bit, e que o nível elétrico do sinal utiliza o padrão RS232, com base na figura que representa a leitura do sinal em um osciloscópio, o dado enviado corresponde a qual valor da tabela ASCII? Considere que o bit menos significativo é enviado primeiro.

Identifique o circuito equivalente somente com portas NOR para o circuito lógico a

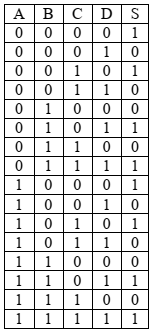

Determine a expressão Booleana melhor simplificada para a saída S, a partir dos valores de entrada (ABCD, sendo A o mais significativo) da tabela verdade abaixo.

Determine a expressão booleana simplificada equivalente.

Y = /(A+B) . ABC + A/B . /(/A/C)

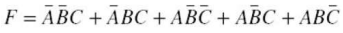

O circuito I é assíncrono, mas pode ser alterado para permitir sincronismo por meio de um sinal de clock.

O circuito I apresenta um elemento de memória do tipo flip-flop JK.

O circuito II é do tipo TTL.

Caso seja conectada, nos terminais A e B, uma fonte de tensão contínua de 100 V e resistência interna de 5 Ω, a corrente iB será 1 A.

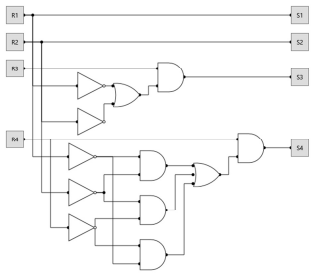

O circuito digital representado faz o controle de acionamento de uma central telefônica que possui quatro ramais. As entradas R1, R2, R3 e R4 significam que o respectivo ramal solicitou uma ligação à central. As saídas S1, S2, S3 e S4 indicam se a ligação foi completada pela central ou não. Considerando esse circuito e as informações apresentadas, julgue o item a seguir.

Considere que, para o circuito lógico combinacional que

compreende as entradas R1, R2, R3 e R4 e a saída R4, se

deseja implementar um circuito com a seguinte regra: o

funcionamento do ramal R4 está condicionado ao não

funcionamento dos ramais R1, R2 e R3 no ciclo de tempo

anterior ao atual. Nesse caso, é necessário o uso de flip-flops

do tipo RS ou JK no módulo de memória do circuito a ser

implementado.

O circuito digital representado faz o controle de acionamento de uma central telefônica que possui quatro ramais. As entradas R1, R2, R3 e R4 significam que o respectivo ramal solicitou uma ligação à central. As saídas S1, S2, S3 e S4 indicam se a ligação foi completada pela central ou não. Considerando esse circuito e as informações apresentadas, julgue o item a seguir.

Para o circuito apresentado, apenas duas ligações podem ser

completadas simultaneamente; os ramais R1 e R2 têm

prioridade sobre o ramal R3; e o ramal R3 tem prioridade

sobre o ramal R4, ao tentar realizar uma chamada.

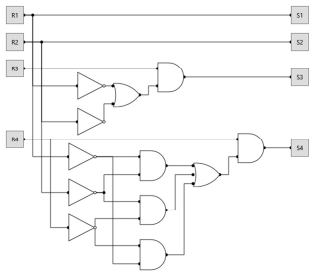

As portas lógicas 1 e 2 são, respectivamente,

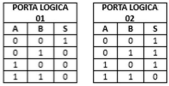

A opção que apresenta uma sequência de entradas A, B, C, D e E, que determina uma saída igual a um, é

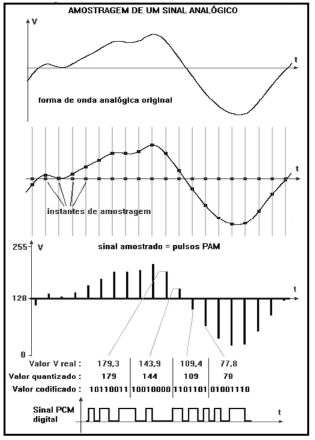

Nesse processo, as três fases para realizar a digitalizar a informação, são, respectivamente,

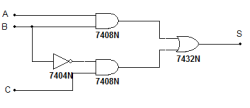

No que diz respeito à eletrônica digital, um circuito lógico é representado por

e expressão de saída

Usando os conceitos do Mapa de Karnaugh, a expressão

simplificada se torna igual a

Esse circuito opera com flip-flop e é denominado