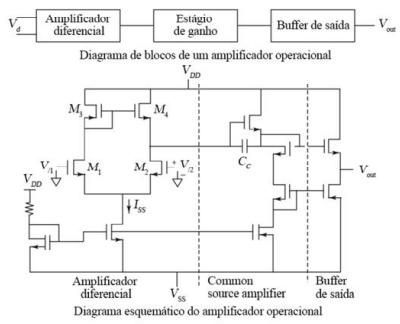

A partir dos diagramas de blocos e esquemático de um amplif...

Próximas questões

Com base no mesmo assunto

Ano: 2024

Banca:

CESPE / CEBRASPE

Órgão:

CTI

Prova:

CESPE / CEBRASPE - 2024 - CTI - Pesquisador Associado I - Especialidade: Tecnologias Habilitadoras - Área de Atuação: Micro e Nanotecnologia |

Q2364406

Engenharia Eletrônica

A partir dos diagramas de blocos e esquemático de um amplificador operacional, apresentados anteriormente, julgue o próximo item.

No processo de design de um amplificador operacional CMOS, a seleção do tamanho dos dispositivos MOSFET e das correntes de polarização tem influência direta em parâmetros tais como ganho, CMRR, dissipação de potência, ruído e taxa de variação (slew rate). Esse processo é iterativo e requer ajustes baseados em simulações, em que aumentar o tamanho dos MOSFETs (aumentando W) com uma menor VGS (tensão entre porta e fonte) pode melhorar o emparelhamento, aumentar o ganho e reduzir o ruído, porém, podendo resultar em uma área de layout maior e potencialmente em menor velocidade de operação.

No processo de design de um amplificador operacional CMOS, a seleção do tamanho dos dispositivos MOSFET e das correntes de polarização tem influência direta em parâmetros tais como ganho, CMRR, dissipação de potência, ruído e taxa de variação (slew rate). Esse processo é iterativo e requer ajustes baseados em simulações, em que aumentar o tamanho dos MOSFETs (aumentando W) com uma menor VGS (tensão entre porta e fonte) pode melhorar o emparelhamento, aumentar o ganho e reduzir o ruído, porém, podendo resultar em uma área de layout maior e potencialmente em menor velocidade de operação.