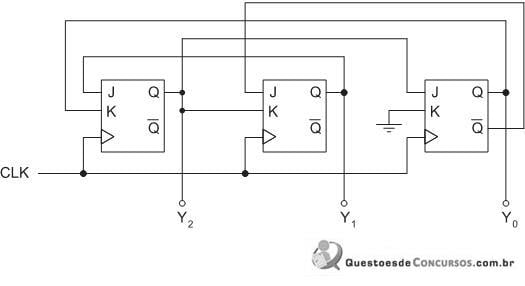

Na figura abaixo, é apresentado o diagrama esquemático de um...

Considerando-se que o circuito inicia sua operação a partir do estado Y2Y1Y0 = 000, sabe-se que o

Comentários

Veja os comentários dos nossos alunos

1 clock= fliflop2 vai para Q=1, pois sua entrada J esta recebendo valor 1 da saída Q' do flipflop 3, e sua entrada K está inicialmente em 0. Já os flip flops 1 e 3 mantêm saídas Q= 0.

logo 010

2 clock= flipflop 1 também vai para 1 pois entrada J foi ativada pela saída Q do flipflop 2 antes de ocorrer a segunda borda de subida do clock;

logo 110

3 clock= flipflop 1 e mantido em 1, flipflop3 vai para 1 pois sua entrada J foi ativada pela saída Q do flipflop 1 antes de ocorrer a terceira borda de subida do clock, flipflop2 vai para 0 devido entrada K receber 1 da saída do flipflop 1 antes do terceiro clock;

logo 101

4 clock= flipflop 1 vai para 0 devido entrada K receber 1 da saída do flipflop 3 antes do quarto clock, flipflop2 mantido em 0 pois entrada K em 1 antes do quarto clock, e flipflop3 mantido em 1 pois entrada J recebendo 1 antes do quarto clock.

logo 001

5 clock em diante: as entradas J e K dos flipflops 1, 2 e 3 são mantidas em 0 para todos os clocks posteriores. Logo fica estagnado na condição 001.

gabarito A:

estado do circuito fica estagnado em Y2Y1Y0 = 001 após 4 ciclos de clock.

Clique para visualizar este comentário

Visualize os comentários desta questão clicando no botão abaixo