Questões Militares

Sobre eletrônica digital em eletrônica

Foram encontradas 197 questões

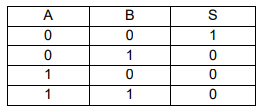

Fonte: IDOETA, Ivan Valeije; CAPUANO, Francisco G. Elementos de Eletrônica Digital. 40ª ed. São Paulo: Érica, 2008. p 49, tabela 2.7.

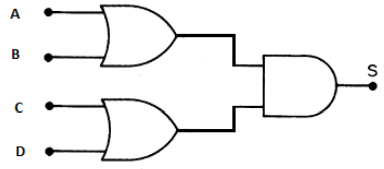

Fonte: IDOETA, Ivan Valeije; CAPUANO, Francisco G. Elementos de Eletrônica Digital. 40ª ed. São Paulo: Érica, 2008. p 52, fig 2.16.

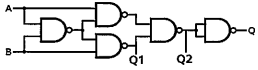

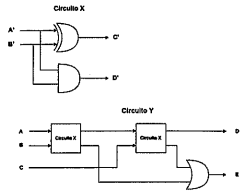

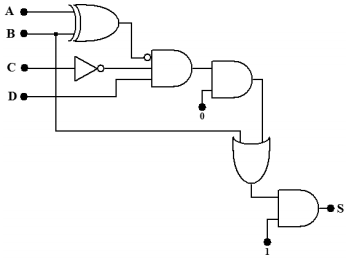

Analise o circuito a seguir.

Com base no circuito combinacional acima, analise as afirmativas abaixo e assinale a opção correta.

I- Q1 = AB +

II- Q2 = A ⊙ B

III-

Analise as figuras a seguir.

Tabela Verdade do Circuito Y

Considerando a tabela verdade e os diagramas

apresentados acima, identifique a função que executa o

circuito Y, sabendo que esse é composto por dois blocos

do circuito X, e assinale a opção correta,

Analise a figura a seguir.

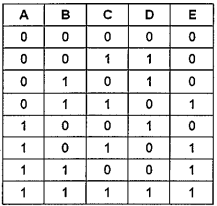

Utilizando-se de 3 flip-flops tipo D (D2D1D0), com mesmo

clock, um circuito combinacional foi criado para

implementar a sequência acima, com seus sinais de saída

representados pelos bits Q2Q1Q0. Fazendo uso da soma

de produtos, a lógica mínima para implementar a entrada

do flip-flop D0 é:

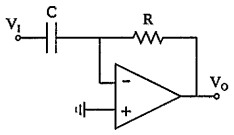

Analise o circuito a seguir.

Sabendo que o circuito acima tem todos os seus componentes ideais, calcule o sinal de saída (Vo) e assinale a opção correta.

Dado:

Sinal de entrada: Vi = e-2t COS (60t)

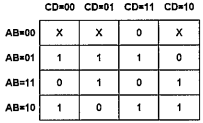

Analise a figura a seguir.

O Mapa de Karnaugh pode ser resolvido por dois

métodos: soma de produtos (SdP) e produto das somas

(PdS). Determine a expressão para Y, pelo método do

produto das somas, do mapa de Karnaugh acima e

assinale a opção correta.

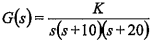

Assinale a opção que apresenta o valor de K tal que o sistema, em malha fechada, seja marginalmente estável, e sua frequência ω de oscilação.

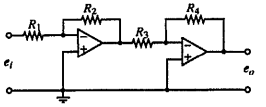

Analise a figura a seguir.

Determine qual é o ganho do circuito com amplificadores

operacionais acima e assinale a opção correta.

A expressão  representa qual circuito lógico?

representa qual circuito lógico?

A expressão booleana S =  pode ser escrita

também da seguinte forma:

pode ser escrita

também da seguinte forma:

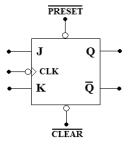

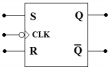

Avalie as informações abaixo com relação ao flip-flop RS ilustrado.

I - O clock é ativado na transição do nível lógico 1 para 0 devido à

presença da inversora.

II - A saída Q não sofre alteração de estado lógico quando as entradas R e S estão em nível lógico 0, independente das transições do clock.

III - O clock tem a função de habilitar as mudanças de estado de saída Q em função das entradas R e S, e esta habilitação ocorre quando o clock mantém-se no nível lógico 0.

IV - As saídas Q e “Q barrado” podem ter o mesmo nível lógico (0 ou 1). Essa condição é obtida pela presença da inversora na entrada de clock com nível lógico 1 aplicado.

Está correto o que se afirma em

Qual das afirmações abaixo está correta com relação ao flip-flop ilustrado?