Questões Militares

Sobre flip-flops em eletrônica

Foram encontradas 29 questões

Analise a figura a seguir.

Utilizando-se de 3 flip-flops tipo D (D2D1D0), com mesmo

clock, um circuito combinacional foi criado para

implementar a sequência acima, com seus sinais de saída

representados pelos bits Q2Q1Q0. Fazendo uso da soma

de produtos, a lógica mínima para implementar a entrada

do flip-flop D0 é:

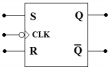

Avalie as informações abaixo com relação ao flip-flop RS ilustrado.

I - O clock é ativado na transição do nível lógico 1 para 0 devido à

presença da inversora.

II - A saída Q não sofre alteração de estado lógico quando as entradas R e S estão em nível lógico 0, independente das transições do clock.

III - O clock tem a função de habilitar as mudanças de estado de saída Q em função das entradas R e S, e esta habilitação ocorre quando o clock mantém-se no nível lógico 0.

IV - As saídas Q e “Q barrado” podem ter o mesmo nível lógico (0 ou 1). Essa condição é obtida pela presença da inversora na entrada de clock com nível lógico 1 aplicado.

Está correto o que se afirma em

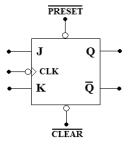

Qual das afirmações abaixo está correta com relação ao flip-flop ilustrado?

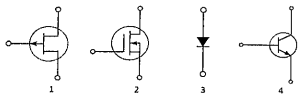

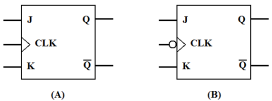

Observe os simbolos padrões abaixo.

Assinale a opção que apresenta a identificação correta

dos simbolos padrões acima.

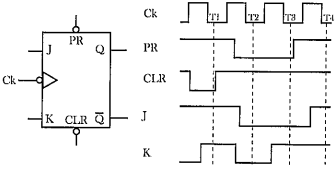

Analise as figuras abaixo.

Em função dos sinais aplicados no flip-flop JK da figura

acima, determine os valores de Q nos tempos T1, T2, T3 e

T4, respectivamente, e assinale a opção correta.

Em relação ao circuito contador binário representado na figura abaixo, marque V para verdadeiro e F para falso. Em seguida, assinale a alternativa com a sequência correta.

( ) É um contador assíncrono de 4 bits desde que todas as entradas J e K estejam em nível lógico 1.

( ) A saída D é o bit mais significativo cuja frequência de alternância entre 0 e 1 é o dobro da frequência do clock aplicado ao circuito.

( ) É um contador síncrono visto que as saídas de cada Flip Flop acionam a entrada de clock do Flip Flop adjacente.

( ) Sendo um contador assíncrono, tem como desvantagem que

as saídas de cada Flip Flop não alteram seu estado lógico no

mesmo instante da transição do clock, sendo que o atraso de

resposta é maior para o bit mais significativo.

Abaixo temos a representação de dois Flip Flops JK (A e B). Observando que a diferença entre o FFA e o FFB está na ausência e presença de um inversor na entrada CLK, respectivamente, qual a diferença operacional entre eles?

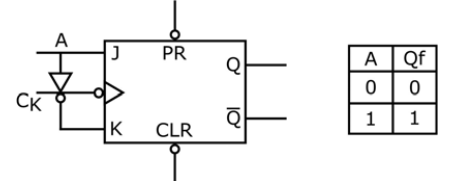

A tabela verdade e o bloco representativo a seguir são referentes ao flip-flop tipo

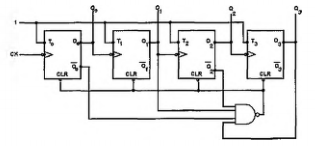

Observe o contador abaixo.

O contador apresentado na figura acima é formado por

quatro flip flops do tipo T e por uma porta NAND de 4

entradas. Os pulsos de contagem se fazem pela entrada

CK e a contagem é dada pelas saídas Q3Q2Q1Q0. Esse

circuito corresponde a um contador:

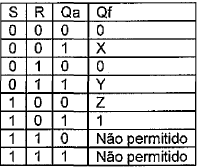

Determine os valores de X, Y e Z, respectivamente, e assinale a resposta correta. Dados: Qa = Estado anterior da saída G. Qf = Estado que a saída deve assumir após aplicação das entradas.

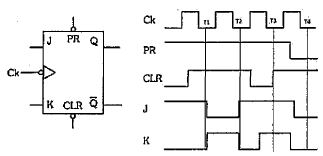

Analise as figuras abaixo.

Em função dos sinais aplicados no flip-flop JK da figura acima, determine os valores de Q nos tempos T1,T2, T3 e T4, respectivamente, e assinale a opção correta.

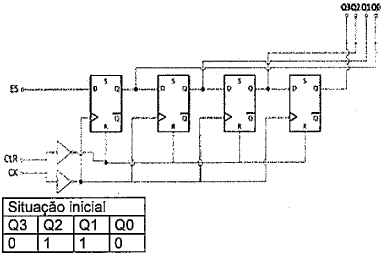

No circuito e situação inicial acima, ES e CLR são mantidos constantes no nível lógico "1" e S em nível lógico “0". Sendo assim, determine a nova situação de saída, Q3 Q2 Q1 Q0, no caso do pulso de clock (CK) aplicado ao circuito possuir duas transições (bordas de descida) negativas, e assinale a opção correta.

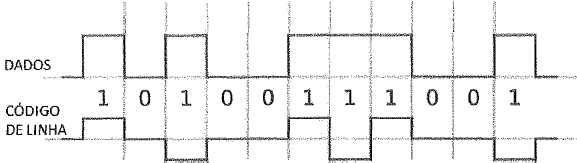

Observe a figura a seguir.

Nos sistemas de comunicação digital, a saída digital do codificador de fonte (dados) é convertida (ou codificada) em pulsos elétricos (formas de onda) para fins de transmissão no canal. Esse processo recebe o nome de codificação de linha. Assinale opção que indica o nome do código de linha digital apresentado na figura acima»

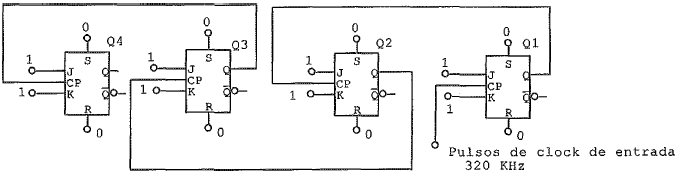

Considere um circuito digital que possui quatro Flip-Flops JK {Q4, Q3, Q2 e Q1) , conforme o diagrama abaixo»

Onde:

S = PRESET

R= CLEAR

CP= CLOCK

Sabendo que pulsos de Clock de 320 KHz são aplicados no FlipFlop

Q1, determine a frequência do sinal de saída (Q) do FlipFlop

Q4 e assinale a opção correta.

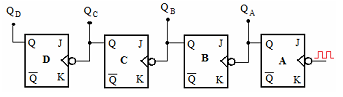

Todas as entradas J e K dos Flip Flops abaixo estão em nível lógico alto. Com base em seus conhecimentos e no circuito abaixo, onde QD é o MSB, pode-se afirmar que

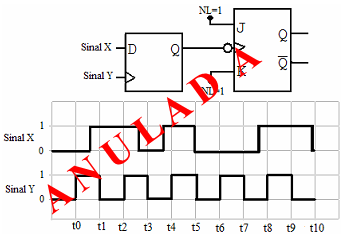

O circuito abaixo é ideal e acionado por borda. No instante t0, a saída Q do Flip Flop JK é igual a 1. Dados: J e K estão com nível lógico 1 (NL=1).

Assinale a alternativa correta.

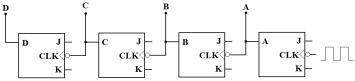

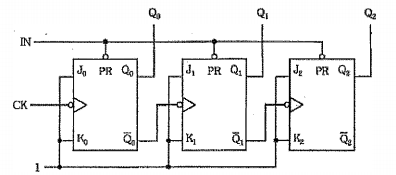

Observe a figura a seguir.

Na figura acima, 3 flip-flops tipo JK são interligados,

sendo as entradas clock do 2° e 3° blocos acionadas pelas

sardas  das anteriores. Que tipo de circuito é representado

por essa figura?

das anteriores. Que tipo de circuito é representado

por essa figura?