Questões Militares de Eletrônica - Flip-Flops

Foram encontradas 29 questões

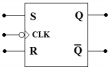

Avalie as informações abaixo com relação ao flip-flop RS ilustrado.

I - O clock é ativado na transição do nível lógico 1 para 0 devido à

presença da inversora.

II - A saída Q não sofre alteração de estado lógico quando as entradas R e S estão em nível lógico 0, independente das transições do clock.

III - O clock tem a função de habilitar as mudanças de estado de saída Q em função das entradas R e S, e esta habilitação ocorre quando o clock mantém-se no nível lógico 0.

IV - As saídas Q e “Q barrado” podem ter o mesmo nível lógico (0 ou 1). Essa condição é obtida pela presença da inversora na entrada de clock com nível lógico 1 aplicado.

Está correto o que se afirma em

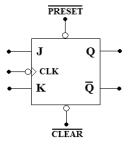

Qual das afirmações abaixo está correta com relação ao flip-flop ilustrado?

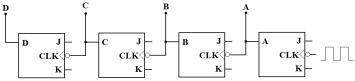

Em relação ao circuito contador binário representado na figura abaixo, marque V para verdadeiro e F para falso. Em seguida, assinale a alternativa com a sequência correta.

( ) É um contador assíncrono de 4 bits desde que todas as entradas J e K estejam em nível lógico 1.

( ) A saída D é o bit mais significativo cuja frequência de alternância entre 0 e 1 é o dobro da frequência do clock aplicado ao circuito.

( ) É um contador síncrono visto que as saídas de cada Flip Flop acionam a entrada de clock do Flip Flop adjacente.

( ) Sendo um contador assíncrono, tem como desvantagem que

as saídas de cada Flip Flop não alteram seu estado lógico no

mesmo instante da transição do clock, sendo que o atraso de

resposta é maior para o bit mais significativo.

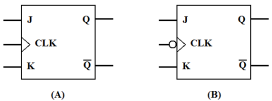

Abaixo temos a representação de dois Flip Flops JK (A e B). Observando que a diferença entre o FFA e o FFB está na ausência e presença de um inversor na entrada CLK, respectivamente, qual a diferença operacional entre eles?