Questões Militares

Para ciaar

Foram encontradas 16.114 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Considere as assertivas abaixo sobre o processo de melhoria da qualidade de software, conhecida como Capability Maturity Model Integrated (CMMI 1.2), em sua versão por estágios.

I. Cada estágio define um conjunto de áreas de processo e objetivos a serem atingidos nessas áreas.

II. Cada estágio alcançado assegura que uma infraestrutura adequada de processo foi implantada, servindo de base para o próximo estágio.

III. Uma organização que, em todos os projetos de desenvolvimento de software, realiza e mantém o planejamento, realiza a gerência dos requisitos, acompanha e controla o progresso e realiza medições que fornecem informações gerenciais encontra-se no estágio 3 de maturidade.

IV. Uma organização que é capaz de gerenciar quantitativamente os projetos de software e analisar e medir o desempenho do processo organizacional, além de atender às exigências dos estágios anteriores, encontra-se no estágio 5 de maturidade.

V. O CMMI por estágios tem como vantagem propiciar às organizações uma abordagem de melhoria provada e prédefinida.

Estão corretas apenas as assertivas:

Analise a descrição do processo de desenvolvimento de software abaixo.

Neste processo organiza-se o desenvolvimento em incrementos, ciclos de desenvolvimento e antes de cada incremento realiza-se uma rodada de planejamento, preferencialmente, com a participação do cliente, para selecionar a próxima funcionalidade a ser construída naquele incremento, ainda para analisar possíveis mudanças no projeto. Cada incremento leva poucas semanas para ser concluído e todos os dias a equipe realiza reuniões curtas no início do dia, para verificar o andamento e se há dificuldades para efetuar o trabalho. No final do incremento, há uma reunião de retrospectiva para avaliar os acertos, os equívocos e o que pode ser melhorado nos próximos ciclos.

Marque a opção que corresponde ao modelo de processo adotado.

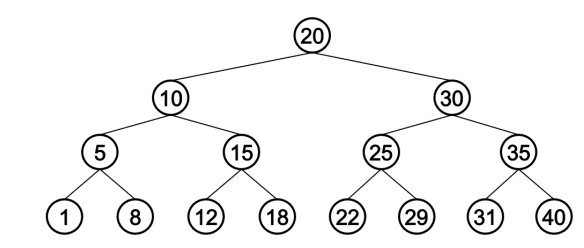

Tomando como ponto de partida a árvore binária de busca balanceada (AVL) abaixo, como será o percurso em pós-ordem dos nós, após os valores 15, 30, 20, 10, 29 terem sido removidos nesta sequência, considerando que a árvore sempre se mantém balanceada? Considere que o balanceamento utiliza o maior nó da subárvore à esquerda.

A opção que traz, de maneira correta, o percurso em pós-ordem dos nós é:

O Real Trip Time (RTT) é um conceito crucial para determinar a integridade de uma rede. É o tempo entre uma solicitação de dados e a exibição desses dados. Dada a definição de RTT, considere o tempo de viagem de ida e volta atual de 42ms. Se as próximas confirmações tiverem valores de 28, 45 e 30ms, respectivamente, quais serão as estimativas RTT? Empregue o algoritmo de Jacobson, considerando α = 0,9.

A opção que contém as estimativas de forma correta é:

Considere o seguinte modelo de dados relacional que representa parte do banco de dados de uma academia, onde as chaves primárias estão sublinhadas.

Aluno (idAluno, nomeAluno)

Participa (idAluno, idAula) idAluno referencia Aluno e idAula referencia

Aula

Aula (idAula, dataAula, horaAula, descricaoAula)

Dentre os códigos SQL abaixo, qual deles retorna todos os alunos que compareceram a pelo menos uma aula e as

datas de cada aula em que os alunos participaram?

O componente central de um computador é o processador, também chamado de unidade central de processamento (CPU). Um processador pode ser classificado de acordo com vários critérios. Um dos critérios de classificação é quanto à utilização de barramentos, se dados e instruções utilizam os mesmos barramentos ou se são separados.

A arquitetura que utiliza barramentos separados para dados e instruções é chamada de arquitetura:

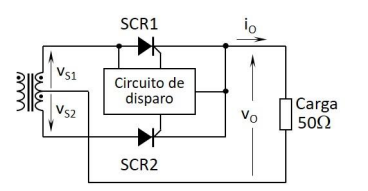

O primário do transformador do circuito, cujo diagrama esquemático abaixo, está ligado a um barramento CA com tensão eficaz de 220 V e frequência de 60 Hz. A relação de espiras do transformador e o ângulo de disparo dos SCRs foram ajustados de tal maneira que, para todos os componentes funcionando corretamente, o valor eficaz da tensão de saída (VO) seja igual a 100 V. Entretanto, o SCR1 desse circuito apresentou um defeito, passando a se comportar permanentemente como um circuito aberto.

Na situação de defeito apresentada, qual é o valor eficaz da tensão de saída?

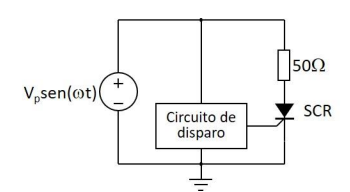

Abaixo é apresentado o diagrama esquemático de um circuito, onde o SCR recebe um pulso de disparo no ângulo ωt = 90º (o mesmo que π/2 radianos). O circuito recebe em sua entrada uma tensão com forma de onda senoidal cujo valor de pico VP = 100π V.

O valor médio da corrente no resistor é igual a:

Uma determinada memória RAM trabalha com uma palavra de dados de 8 bits e tem um sistema de endereçamento multiplexado em duas etapas, controlado por dois sinais, RAS e CAS. Inicialmente, o barramento de endereço dessa memória recebe 5 bits de endereço de linha e o sinal RAS é pulsado. Depois, o barramento de endereço recebe 6 bits de endereço de coluna e o sinal CAS é pulsado.

Qual é a capacidade dessa memória em bytes?

Analise as afirmativas abaixo quanto aos dispositivos lógicos programáveis (PLD):

I. Um PLD do tipo arranjo lógico programável (PLA) tem um arranjo de portas AND/OR e são programáveis com a queima de fusíveis em uma matriz, com a vantagem de serem totalmente reprogramáveis.

II. Os dispositivos lógicos programáveis complexos (CPLD) que empregam tecnologia de programação EEPROM são apagáveis, reprogramáveis e não voláteis.

III. PLDs do tipo matrizes de portas programáveis em campo (FPGA) podem utilizar uma tabela de consulta (LUT) para criar as funções combinacionais desejadas, sendo que uma LUT de N entradas funciona como uma tabela-verdade para 2N-1 combinações possíveis.

IV. Os FPGAs baseados em SRAM necessitam, para a sua configuração, de uma memória externa cujo conteúdo é transferido para o FPGA quando o dispositivo é energizado.

V. Uma diferença entre CPLD e FPGA é que, no primeiro, os recursos internos de roteamento de sinal lógico programável tendem a ser uniformes em todo o chip, produzindo atrasos de sinal consistentes, enquanto que, no segundo, tendem a ser bem variados, com extensões de caminhos diferentes disponíveis e, portanto, atrasos diferentes.

Sobre as afirmativas acima, é correto afirmar que:

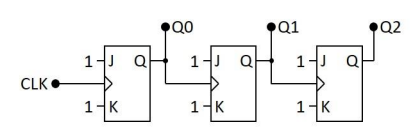

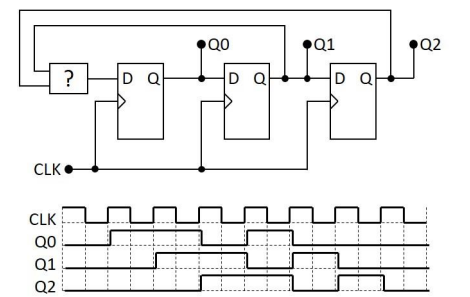

Sabendo-se que, em um determinado instante, o valor binário das saídas Q2Q1Q0, tomadas nessa ordem, é igual a 010, qual o valor binário das saídas após 5 ms?

O circuito cujo diagrama esquemático abaixo apresenta um circuito composto por três flip-flops e uma porta lógica desconhecida.

Para que o circuito funcione conforme o diagrama temporal acima, o bloco marcado com uma interrogação deve ser

substituído por uma porta:

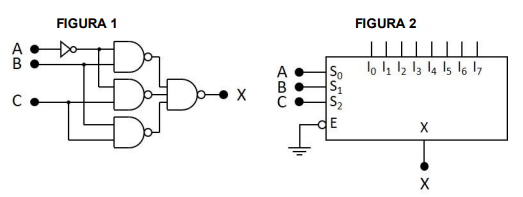

A forma de onda que corresponde corretamente à saída X do circuito mostrado é:

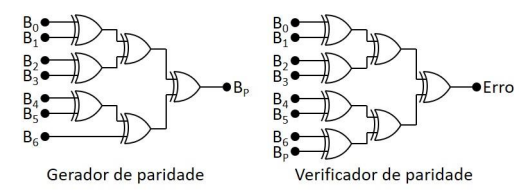

2O projetista de uma empresa foi encarregado de projetar um circuito gerador de paridade par para uma palavra de sete bits. Um outro projetista foi encarregado de projetar um circuito verificador de paridade para trabalhar com dados com paridade ímpar e que deve gerar um sinal de erro com nível lógico alto se houver erro em um dos bits recebidos.

Analise abaixo os diagramas esquemáticos dos dois circuitos projetados.

Sobre os circuitos acima, e considerando-se as especificações de cada um, é correto afirmar que:

Analise abaixo os diagramas esquemáticos de dois circuitos, sendo o que primeiro emprega portas lógicas e o segundo, um multiplexador com oito entradas, onde I0 a I7 são as entradas de dados, S0 a S2 são as entradas de seleção, sendo S2 a mais significativa e E é uma entrada de habilitação ativa em nível lógico baixo.

As entradas do multiplexador podem ser ligadas ao nível lógico baixo (0) ou nível lógico alto (1). Para que o circuito

com o multiplexador seja funcionalmente equivalente ao circuito com portas lógicas, ou seja, para que a cada uma

das possíveis combinações das entradas ambos os circuitos tenham saídas iguais, as entradas do multiplexador I0 a

I7 deverão ser ligadas, respectivamente, a:

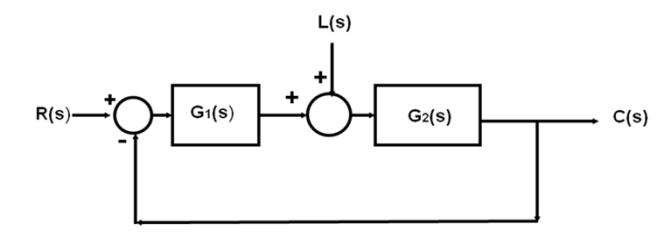

Considere o sistema de controle representado pelo diagrama em blocos abaixo, sendo C(s) a saída do sistema, R(s) o valor do set-point e L(s) o distúrbio.

Pode-se afirmar que, para o sistema de controle regulatório, sendo R(s) = 0, a função de transferência do sistema

será dada por:

Ao aplicar-se uma função de grau r(t) com amplitude 5 à entrada de um sistema de controle por realimentação negativa, representado pela função de transferência Gp(s), obtem-se a resposta temporal: c(t) = 3∙t.

Considere:

Em relação à estabilidade do sistema de controle, é correto afirmar que:

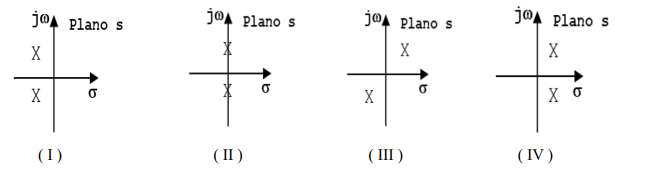

A estabilidade de um amplificador ou outro sistema é determinada diretamente por seus polos.

Analise abaixo os quatro planos s onde os X mostram as diferentes posições dos polos.

O plano s que mostra os polos localizados na posição em que uma excitação por um impulso unitário na entrada

gera, como resposta, uma oscilação sustentável é indicado em:

Um trecho de uma linha de transmissão operando na faixa de frequências de micro-ondas é terminado em curto-circuito. Considere as perdas na linha desprezíveis e sua impedância característica igual a 50 Ohms. Sabe-se que, nesta situação, a impedância vista na entrada desse trecho de linha vai depender do seu comprimento físico.

Se o trecho tem exatos ¼ do comprimento de onda, a impedância vista na entrada deve ser: