Questões de Concurso Sobre engenharia eletrônica

Foram encontradas 3.780 questões

O mencionado codificador consumirá menos energia se for construído com componentes CMOS que se construído com componentes de lógica TTL.

A figura I acima ilustra, esquematicamente, uma rede de comunicações, e a figura II, um enlace entre os sítios A e T, que contêm os dados de geometria, frequência, potência de transmissão no sítio A e potência de recepção no sítio B. Nesse enlace, há uma obstrução do tipo gume de faca, a qual provoca atenuação do sinal, conforme indicado no gráfico apresentado na figura III. Antenas idênticas são utilizadas nos sítios A e T, cujos diagramas de radiação e direção do enlace estão apresentados na figura IV.

Com base nessas informações, julgue os itens

A figura I acima ilustra, esquematicamente, uma rede de comunicações, e a figura II, um enlace entre os sítios A e T, que contêm os dados de geometria, frequência, potência de transmissão no sítio A e potência de recepção no sítio B. Nesse enlace, há uma obstrução do tipo gume de faca, a qual provoca atenuação do sinal, conforme indicado no gráfico apresentado na figura III. Antenas idênticas são utilizadas nos sítios A e T, cujos diagramas de radiação e direção do enlace estão apresentados na figura IV.

Com base nessas informações, julgue os itens

A memória RAM possibilita a leitura rápida de dados pelo computador, porém os dados nela armazenados são apagados assim que a máquina é desligada. A memória ROM, contudo, é não volátil e retém todos os programas necessários para o boot do computador durante o carregamento do sistema operacional.

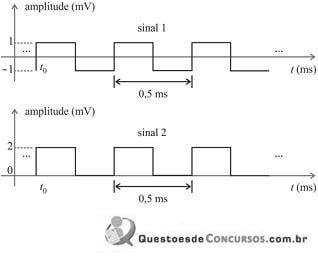

Se os sinais 1 e 2 ilustrados abaixo, de mesma amplitude pico-a-pico, fase e período, forem processados por um osciloscópio digital de 1 GHz de largura de faixa e canais de aquisição com acoplamento CC, então as suas transformadas rápidas de Fourier (FFT) serão iguais.

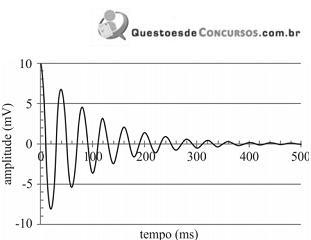

Considere o gráfico abaixo, que representa a resposta impulsiva de um sistema dinâmico linear de segunda ordem em uma janela temporal de cinco constantes de tempo. Nessa situação, o sistema pode ser corretamente caracterizado por um par de polos complexos conjugados com valores aproximados de -10 + j50p e -10 - j50p.

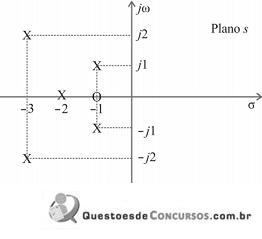

Se a figura abaixo representa o mapa de polos (identificados por ‘x’) e zeros (identificados por ‘0’) de uma função de transferência em malha fechada de um sistema dinâmico linear, então o sistema é estável e gera uma saída com amplitude não nula, em regime permanente, quando a entrada é uma função do tipo degrau.

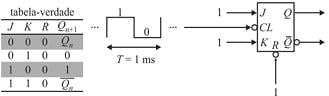

A figura abaixo ilustra um flip-flop JK mestre-escravo, em que J e K são os terminais de entrada; CL é a entrada de clock; R, o terminal de reset; e Q e

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

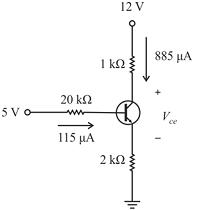

No circuito analógico abaixo, que contém um transistor bipolar de junção do tipo NPN polarizado no modo ativo, a tensão entre coletor e emissor é superior a 8 V e inferior a 10 V.

Na polarização de circuitos integrados lógicos das famílias TTL (transistor-transistor logic) e CMOS (complimentary metal-oxide-semiconductor), são geralmente empregadas fontes de tensão contínua de 10 V.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se, na entrada do conversor A/D, o sinal tiver amplitude de 2 V eficaz e a relação sinal-ruído (SNR) for de 40 dB, então o amplificador terá ganho G igual a 2.000 e a amplitude do ruído será inferior a 10 mV eficaz.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se a tensão de referência do conversor A/D for Vref = 5 V, então a resolução correspondente será inferior a 2 mV.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Para que o conversor A/D não distorça o sinal de entrada, é necessário que a taxa de amostragem mínima seja de 2 × 106 amostras por segundo.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Considere que a resposta em frequência da associação entre buffer e amplificador seja máxima e constante na faixa espectral compreendida entre 1 kHz e 500 MHz. Considere, ainda, que a banda passante dessa associação seja ajustável e possa ser selecionada entre dois valores: 200 MHz e 400 MHz. Nessa situação, a SNR será mínima se o valor de 200 MHz for escolhido para a largura de faixa da associação.

Os circuitos Schmitt-Triggers são utilizados para o acoplamento de dispositivos lentos e dispositivos rápidos. Esses circuitos deixam mais lentas as variações de um sinal rápido, permitindo, assim, o acoplamento de circuitos da família CMOS, mais rápidos, com circuitos da família TTL, geralmente mais lentos

Tanto a família TTL (Transistor-Transistor Logic) como a família ECL (Emitter-Coupled Logic) utilizam transistores bipolares em sua construção; no entanto, a família ECL possui maior velocidade de comutação em comparação com a família TTL.

Se uma porta lógica possuir fator de carga igual a oito, suportará em sua entrada, sem sofrer danos, uma tensão de até oito vezes o valor da tensão de nível lógico

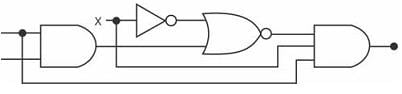

O circuito representado na figura abaixo pode ser implementado de maneira mais eficiente utilizando-se apenas uma porta NOT e uma porta AND.

O ciclo de varredura de um CLP, após sua inicialização, consiste na verificação do estado das entradas, na transferência de dados para a memória imagem das entradas e saídas, na comparação com o programa do usuário e na atualização das saídas.