Questões de Concurso

Sobre arquitetura de processadores: risc, cisc, wisc e microprocessadores. em arquitetura de computadores

Foram encontradas 330 questões

Considere que programa tem 1.000.000 (M) de instruções. Em uma arquitetura sem pipeline, o tempo médio de execução de cada instrução (t1) é 6,5 ns. Nesta arquitetura, o tempo gasto no processamento das M instruções é: T1 = 6,5 ns * 1.000.000 ≅ 6,5 ms. O ganho (T1/T2) na execução deste programa em um processador com pipeline de 5 estágios com ciclo de 2 ns (t2) é:

I. Na arquitetura CISC, o comprimento das instruções é fixo; no RISC, é variável.

II. O número de registradores no CISC é tipicamente baixo, de 1 a 8; no RISC, é tipicamente alto, de 64 a 128.

III. Na execução, as instruções o CISC tem baixa superposição; no RISC, é alta superposição baseada em pipeline.

Está correto o que se afirma apenas em

Quanto à memória secundária, aos barramentos de entrada e saída e às arquiteturas RISC e CISC, julgue o item.

As máquinas RISC tendem a executar instruções com maior rapidez que as máquinas CISC.

Quanto à memória secundária, aos barramentos de entrada e saída e às arquiteturas RISC e CISC, julgue o item.

O pipelining é utilizado somente em arquiteturas RISC.

Quanto à memória secundária, aos barramentos de entrada e saída e às arquiteturas RISC e CISC, julgue o item.

A principal função dos barramentos de entrada e saída é

interligar os periféricos do computador, de modo a

permitir a troca de mensagens entre eles; por serem

dispositivos lógicos, eles não viabilizam a

compatibilidade entre os periféricos.

Quanto à memória secundária, aos barramentos de entrada e saída e às arquiteturas RISC e CISC, julgue o item.

Nos discos magnéticos, os dados são gravados e, mais

tarde, recuperados por meio de uma bobina condutora,

chamada cabeça.

Quanto à memória secundária, aos barramentos de entrada e saída e às arquiteturas RISC e CISC, julgue o item.

Diferentemente dos discos magnéticos — em que os

dados são lidos e gravados em blocos contíguos —, nas

fitas magnéticas, eles são lidos e gravados em blocos não

contíguos, já que elas usam a gravação

paralela (gravação nos dois lados da fita).

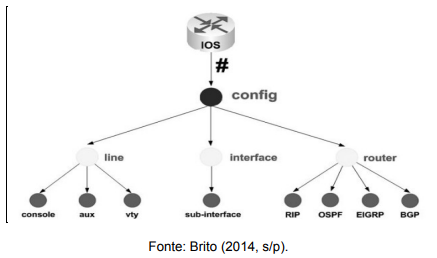

Observe a figura a seguir, que representa os modos de configuração mais comuns do Cisco/IOS.

A respeito desses modos de configuração, é CORRETO afirmar que

Leia a frase abaixo referente às duas grandes linhas de arquitetura de processadores.

"Enquanto o CISC possui um ______ conjunto de ______, o RISC possui um conjunto ______ de ______"

Assinale a alternativa que preencha correta e

respectivamente as lacunas:

Com relação a servidores de aplicação, arquitetura de rede TCP/IP e arquitetura hardware de servidores, julgue o item subsequente.

Um processador RISC (Reduced Instruction Set Computer)

usa formatos variáveis de instrução e um pequeno conjunto

de registradores de uso geral. O conjunto de instruções

desses computadores contém cerca de 120 a 350 instruções,

cada uma delas tendo as características necessárias para ser

executada em vários ciclos de relógio.

Acerca de RISC e CISC, julgue o item a seguir.

Uma arquitetura com conjunto de instruções RISC utiliza a

técnica de desvio atrasado, na qual instruções de desvio são

rearranjadas com outras instruções para melhorar a eficiência

do pipeline.

Acerca de RISC e CISC, julgue o item a seguir.

O CISC possui como características operações registrador-para-registrador, uma instrução por ciclo de clock e um

número maior de instruções, bem como instruções mais

complexas, quando comparado ao RISC.

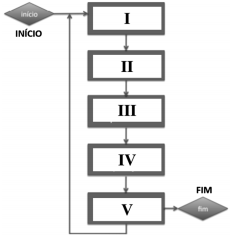

Sendo as fases I – buscar instrução na memória principal e V – armazenar resultado, as demais fases II,III e IV são, respectivamente:

Acerca de hardware, julgue o item a seguir.

A arquitetura CISC tem como desvantagem a impossibilidade

de se alterar alguma instrução composta. No RISC, o código

equivalente às instruções compostas do CISC pode ser escrito

usando-se um conjunto de instruções simples, para melhorar o

desempenho da máquina.

Acerca de organização e arquitetura de computadores, julgue o item que se segue.

Uma máquina embasada na arquitetura CISC faz mais uso do

pipelining que uma máquina com arquitetura RISC.