Questões de Concurso Sobre arquitetura de computadores

Foram encontradas 6.341 questões

Caso um projetista de microprocessadores deseje desenvolver um novo microprocessador com arquitetura do tipo RISC, ele deverá desenvolver o maior conjunto possível de instruções e o maior número possível de formatos, de forma que o número de instruções executadas em cada programa seja mínimo.

Em computadores que utilizam barramento de dados para a comunicação entre o microprocessador e outras partes do microcomputador, tais como as memórias e os dispositivos de entrada e saída, não é possível conectar portas de três estados ao barramento de dados, visto que portas que assumem o estado de alta impedância não devem ser ligadas a esse tipo de barramento.

A capacidade de geração eficiente de códigos objetos pode aumentar a eficiência do pipeline, caso as instruções em código de máquina sejam ordenadas de forma adequada; portanto, em computadores que utilizam essa técnica, a qualidade dos compiladores é um fator relevante.

O tamanho da memória ROM é inferior a 1.000 bytes.

Para endereçar todos os endereços de memória RAM, será necessário utilizar pelo menos 10 linhas de endereço, além das linhas de controle de leitura e escrita.

Caso a memória RAM seja dinâmica, não será necessário incluir, na implementação do computador, circuitos que propiciem sinais de refresh.

A parte volátil da memória possui tamanho maior do que a parte não volátil.

O tamanho total da memória, incluindo ROM e RAM, é superior a 30.000 bytes.

O tamanho da memória RAM é superior a 2.000 bytes.

I. Consiste de vários processadores semelhantes dentro de um mesmo computador, interconectados por um barramento ou algum tipo de arranjo de comutação.

II. Consiste em um grupo de computadores completos e interconectados trabalhando juntos, como um recurso computacional unificado que pode criar a ilusão de ser apenas uma máquina.

I e II são, respectivamente,

I. Um grande número de registradores de propósito geral e/ou o uso de tecnologia de compiladores para otimizar o uso de registradores.

II. Um conjunto de instruções simples e limitado, com formato fixo.

III. Ênfase na otimização do pipeline de instruções.

IV. Instruções de máquina interpretadas por um microprograma localizado em uma memória do circuito integrado do processador.

Embora os sistemas RISC tenham sido definidos e projetados de muitas maneiras e por grupos diferentes, os elementos compartilhados pela maioria dos projetos são os descritos APENAS em

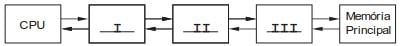

I, II e III representam níveis de cache com as seguintes características:

Tamanho Velocidade

I 32 KB Muito rápida

II 256 KB Mais lenta que I

III 8 MB Mais lenta que II

Desta forma I, II e III representam, respectivamente, memórias cache

( ) Os dados e as instruções são armazenados em várias memória de leitura e escrita.

( ) O conteúdo dessa memória é endereçado pela sua posição, independentemente do tipo de dados nela contido.

( ) A execução de instruções ocorre de modo matricial, exceto quando o programa altere a instrução para a seguinte.

A sequência correta é: