Questões de Concurso Sobre arquitetura de computadores

Foram encontradas 6.341 questões

No SMP (Symetric Multiprocessors), em um sistema fortemente acoplado, constata-se que

Essa técnica chama-se

Observa-se que o conteúdo de natureza volátil se refere

Entre outros componentes, além da unidade lógica e aritmética (ULA), da unidade de controle (UC), e dos registradores, os microprocessadores mais sofisticados têm uma unidade de ponto flutuante que permite a realização de cálculos mais complexos do que a ULA, podendo até substituir totalmente as funções de processamento geral dessa unidade.

Nos computadores atuais, componentes diferentes podem ter níveis diferentes de acesso ao processador, sendo separados por barramentos de comunicação distintos, em que são utilizados, por exemplo, um ou mais barramentos de alta velocidade, que conectam dispositivos que permitem altas taxas de comunicação com a CPU, como a memória principal, as placas gráficas, alguns controladores de discos mais rápido se um ou mais barramentos para componentes que demandam comunicações mais lentas, como saídas de som, impressoras, modems, entre outros.

O tamanho dos registradores internos de um processador de 64 bits é o dobro com relação a um processador de 32 bits, o que não garante que o primeiro processe, necessariamente, o dobro de dados por ciclo de clock com relação ao segundo.

Considerando que cada posição endereçável da memória consiste em 1 byte, um endereço de memória de 32 bits permite endereçar uma memória de

PORQUE

O propósito de um barramento de serviços corporativos é fornecer interoperabilidade juntamente com serviços adicionais, tais como segurança e monitoramento.

Analisando-se as afirmações acima, conclui-se que

Nesse contexto, quais tecnologias são fundamentais para a implantação de um ESB aberto?

Um processador hipotético tem dois registradores de uso geral X e Y, ambos de 8 bits. As instruções desse processador têm um formato de tamanho fixo de 32 bits, dos quais os 8 mais significativos, ou seja, os primeiros lidos da memória durante a busca, são utilizados para o OpCode e os 24 restantes para operandos. Uma das operações desse processador, cujo OpCode é igual a 10110100, utiliza dois operandos: o primeiro é imediato de 8 bits e o segundo utiliza os 16 bits restantes para um endereçamento direto. O resultado da execução dessa operação é colocar a soma dos dois operandos no registrador X. Os operandos são inteiros de 8 bits e utiliza-se o complemento a 2.

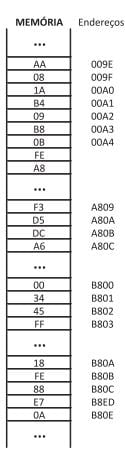

Considere que a próxima instrução a ser executada está no endereço 00A1. O conteúdo da memória, nesse instante, está ilustrado na Figura. Como resultado da operação, o registrador X conterá o valor, em base decimal, de

• 1 bit de overflow (V)

• 1 bit de carry (C)

• 1 bit indicativo de resultado negativo (N) (1 caso o resultado da última operação tenha sido < 0)

• 1 bit indicativo de resultado zero (Z) (1 caso o resultado da última operação tenha sido = 0)

O registro de FLAGS tem, como bit mais significativo, V, seguido pelo C, N e Z. Em um determinado instante, os valores em hexadecimal armazenados em ALUx e ALUy são, respectivamente A000 e 804A. Nesse momento, a Unidade de Controle (UC) do processador envia um sinal de controle acionando a operação de soma da ULA.

Como resultado, o registro de FLAGS conterá, em binários, o valor

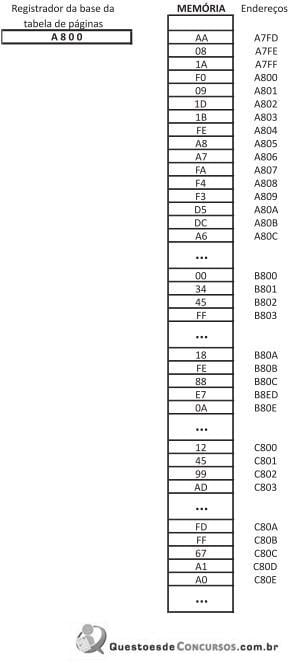

Em um determinado sistema que utiliza paginação de memória, endereços lógicos foram projetados com 16 bits, dos quais os 4 mais significativos indicam uma entrada na tabela de páginas. Nesse sistema existe um registrador especial que contém o endereço do início da tabela de páginas, que está armazenada na memória e contém 16 entradas, cada uma com 8 bits. Em cada entrada dessa tabela de páginas, os quatro bits mais significativos (os da esquerda) são bits de controle e os quatro restantes correspondem aos 4 bits mais significativos do endereço da página física de memória. Considere que o conteúdo da memória e do registrador do início (base) da tabela de páginas é o da figura, na qual todos os valores encontram-se representados em hexadecimal.

Um acesso de leitura ao endereço lógico B80A retornará, em hexadecimal, o valor