Questões de Concurso

Sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 891 questões

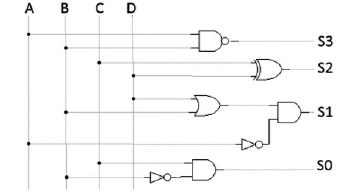

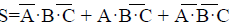

Assinale a alternativa que contém a melhor simplificação para a expressão lógica

A mensagem binária 10100111, representada pelos níveis de sinal mostrados na figura A acima, será transmitida. Para essa finalidade, são projetados circuitos digitais para separar os bits em grupos de dois, na medida em que eles chegam em série do computador, sendo alocado, para cada par, um entre quatro níveis de tensão possíveis. Assim, aos pares binários (00), (01), (10) e (11) são atribuídas as tensões 0 V, 1 V, 2 V e 3 V, respectivamente. Dessa forma, para enviar a mensagem binária 10100111, o sistema quaternário desenvolvido deve transmitir 2 V, 2 V, 1 V e 3 V, conforme ilustrado na figura B acima. Com base nessas informações, julgue o item seguinte.

A taxa de relógio (clock) do computador necessária para

transmissão binária é a metade da taxa de relógio do

computador para transmissão quaternária.

A mensagem binária 10100111, representada pelos níveis de sinal mostrados na figura A acima, será transmitida. Para essa finalidade, são projetados circuitos digitais para separar os bits em grupos de dois, na medida em que eles chegam em série do computador, sendo alocado, para cada par, um entre quatro níveis de tensão possíveis. Assim, aos pares binários (00), (01), (10) e (11) são atribuídas as tensões 0 V, 1 V, 2 V e 3 V, respectivamente. Dessa forma, para enviar a mensagem binária 10100111, o sistema quaternário desenvolvido deve transmitir 2 V, 2 V, 1 V e 3 V, conforme ilustrado na figura B acima. Com base nessas informações, julgue o item seguinte.

A taxa de transferência e a taxa de baud da transmissão

quaternária correspondem, respectivamente, ao dobro da taxa

de transferência e ao dobro da taxa de baud da transmissão

binária.

Um esquema para detecção de dados é a paridade, uma técnica utilizada para detecção de ocorrência de erros em uma transmissão digital de sinais. O circuito acima foi projetado para examinar os bits 1 de cada palavra digital transmitida e produzir bit 1 ou 0 adicional para que o total de bits 1 resulte par (paridade par) ou ímpar (paridade ímpar). O mesmo circuito pode ser usado para verificação de paridade no receptor: nesse local, caso a verificação de paridade seja falsa, significa que ocorreu um erro de transmissão. Nesse esquema específico, a palavra digital de sete bits é acoplada, bit a bit, nas entradas de e1 a e7. Os bits adicionais, disponíveis nos terminais Pi e Po, determinam a paridade da palavra digital. De acordo com essas informações e com a figura apresentada acima, julgue o próximo item.

Para uma verificação válida (verdadeira), a fim de que o

circuito funcione como um verificador de paridade ímpar, o bit

correspondente ao terminal Po deverá ser 0.

Um esquema para detecção de dados é a paridade, uma técnica utilizada para detecção de ocorrência de erros em uma transmissão digital de sinais. O circuito acima foi projetado para examinar os bits 1 de cada palavra digital transmitida e produzir bit 1 ou 0 adicional para que o total de bits 1 resulte par (paridade par) ou ímpar (paridade ímpar). O mesmo circuito pode ser usado para verificação de paridade no receptor: nesse local, caso a verificação de paridade seja falsa, significa que ocorreu um erro de transmissão. Nesse esquema específico, a palavra digital de sete bits é acoplada, bit a bit, nas entradas de e1 a e7. Os bits adicionais, disponíveis nos terminais Pi e Po, determinam a paridade da palavra digital. De acordo com essas informações e com a figura apresentada acima, julgue o próximo item.

Para que o circuito funcione como gerador de paridade, o

terminal Pi

deve ser ligado ao terra do circuito, para geração de

paridade ímpar, ou à fonte de alimentação do circuito, para

geração de paridade par.

Com relação a sistemas e dispositivos digitais, julgue o item seguinte.

No flip-flop JK do tipo mestre-escravo, se as entradas J e K

estiverem todo o tempo conectadas ao nível lógico 1, então a

saída Q, após sucessivos ciclos de relógio, permanecerá no

nível lógico 1.

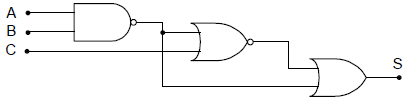

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

O circuito utiliza uma porta lógica do tipo ou exclusivo.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

A expressão lógica resultando na saída S = [AB + (A+B)]E

descreve corretamente a relação entre a saída e as entradas do

circuito.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se as portas TTL usadas no circuito forem do tipo HS, elas

terão um tempo de comutação, de um estado para outro, muito

maior do que se as portas forem do tipo LS, e o consumo de

potência das portas do tipo HS será menor do que o consumo

das portas do tipo LS.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se a entrada E assumir o valor 1, então a saída S assumirá o

valor 1, independentemente dos valores assumidos pelas

variáveis A, B, C e D.

Considere que o circuito combinacional mostrado na figura acima seja implementado com portas lógicas com tecnologia TTL. Suponha que as entradas do circuito sejam representadas pelas variáveis A, B, C, D e E e que a saída do circuito seja representada pela variável S. Com relação a esse circuito, julgue o item subsequente.

Se as entradas A, B, C, D e E assumirem, respectivamente, os

valores 1, 1, 0, 1 e 1, então a saída S assumirá o valor 1.