Questões de Engenharia Eletrônica - Eletrônica Digital na Engenharia Eletrônica para Concurso

Foram encontradas 888 questões

Diferentemente de sistemas PDH, na hierarquia digital síncrona (SDH – synchronous digital hierarchy) todos os elementos de rede devem usar a mesma referência de clock.

O esquema TDM é usualmente aplicado em sinais analógicos.

A transmissão de dados na Internet se baseia no conceito de comutação por circuitos.

Diferentemente da multiplexação por divisão da frequência (FDM – frequency division multiplexing), a multiplexação por divisão do tempo (TDM – time division multiplexing) não necessita de banda de guarda entre os diferentes sinais multiplexados.

No esquema de multiplexação por divisão de códigos (CDM – code division multiplexing), diferentes sinais podem ser enviados na mesma frequência e ao mesmo tempo, sendo, para isso, necessário realizar espalhamento espectral, em que a banda ocupada pelo sinal é aumentada pelo uso de um código.

O dispositivo PAL (programmable array logic), ou matriz lógica programável, é em um arranjo programável de portas XOR, que se conecta a um arranjo fixo de portas AND.

Em um multiplexador que seleciona as informações, os dados são transferidos de uma linha para diversas linhas.

Glitch é um pulso de tensão ou de corrente de curta duração que pode ser interpretado, por um circuito lógico, como um sinal válido e provocar uma operação inadequada.

Para converter números representados na base octal em números binários, deve-se separar cada dígito do número octal e substituí-lo por seu valor correspondente binário de quatro bits.

Para efetuar operações aritméticas binárias, a adição de um número positivo com um número negativo maior resulta em um número negativo em complemento de 2.

O tempo de conversão de um conversor A/D por aproximações sucessivas aumenta à medida que a tensão analógica de entrada aumenta.

No que se refere a conversores analógico-digital (A/D) e digital-analógico (D/A), julgue o item subsecutivo.

A saída de um conversor D/A de 5 bits pode produzir 32 níveis diferentes de tensão

Conversores A/D flash não utilizam sinal de clock, visto que não necessitam de temporização ou sequenciamento.

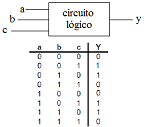

Esse circuito possui entradas a, b e c. A saída y desse circuito é:

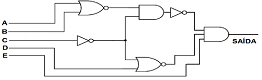

Para que a saída seja igual à unidade, a sequência de entradas A, B, C, D e E deve ser:

PORT (a, b, c: IN bit;

d, e: OUT bit);

END entidade;

ARCHITECTURE arquitetura OF entidade IS

BEGIN

PROCESS (a, b, c)

BEGIN

IF (c = '1') THEN

d <= a XOR b;

e <= a AND b;

ELSE

d <= '0';

e <= '0';

END PROCESS;

END arquitetura;

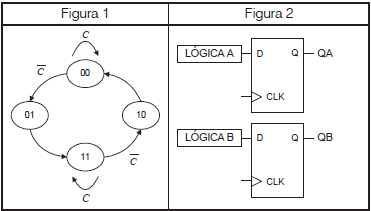

A Figura 1, acima, mostra um diagrama de quatro estados definidos pelos bits B e A, sendo B o mais significativo, e pelo bit de controle C.

A Figura 2, por sua vez, mostra uma implementação síncrona desse diagrama de estados com o uso de flip-flops D e das lógicas A e B.

Estas lógicas devem ser, respectivamente:

Contador Flip-Flop JK

A figura acima mostra um contador binário conectado a um flip-flop JK, ambos com entrada de clock acionada por borda. O contador está programado para decrementar (D/U = 1) e, no início da contagem, Q = Q1 = Q0 = 0, sendo Q1 mais significativo do que Q0. Além disso, cada pulso de clock do contador (Clk1) é seguido por um pulso de clock do flip-flop (Clk2), havendo tempo suficiente para a estabilização das saídas de ambos os dispositivos.