Questões de Concurso

Sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 911 questões

quando truncada para N bits, vale

Há, porém, uma técnica ou equipamento mais adequado para transmitir, em um mesmo canal, mais de um sinal, simultaneamente, evitando os problemas mencionados, que é a(o)

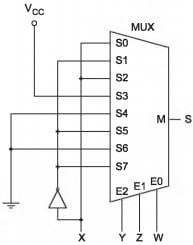

W= XYZ + XYZ + X YZ + XYZ + XYZ + XYZ

A expressão simplificada de W é

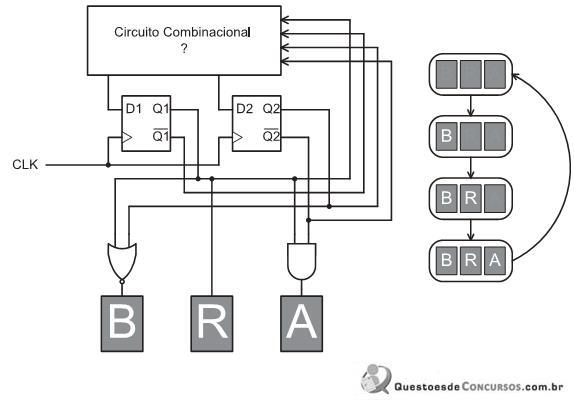

Esse circuito foi projetado de modo que uma determinada letra acenderá somente quando o seu respectivo sinal de comando digital assumir um nível lógico alto.

O objetivo desse circuito é fazer com que as letras acendam e apaguem, repetindo a ordem mostrada pelo diagrama apresentado. Nessa sequência, as três começam apagadas, e, depois, as letras vão acendendo uma a uma até que todas estejam acesas ao final da sequência.

Para realizar a sequência de acendimento desejada, o circuito combinacional deve produzir os sinais de comando dos flip-flops tipo D, através do seguinte par de funções lógicas:

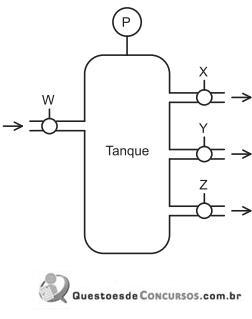

Nesse sistema, a válvula W deve ser aberta para permitir a entrada de gás, sempre que duas ou mais válvulas de saída estiverem abertas, ou quando a pressão no interior do tanque estiver abaixo do mínimo desejado.

Qual é o circuito digital que deve ser usado para produzir o sinal de comando da válvula W?

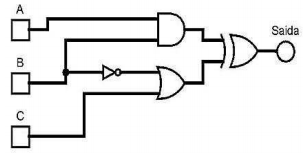

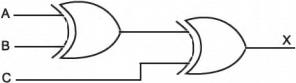

Com base no circuito lógico apresentado, assinale a alternativa correta.

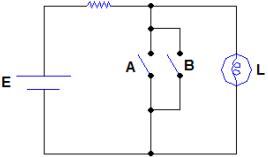

A Lâmpada L será a saída e assumirá o valor 1 (um) se estiver acesa e 0 (zero), se apagada. A porta lógica que esse circuito está representando é

Sua saída é representada pela seguinte expressão:

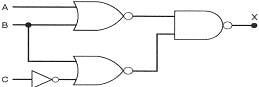

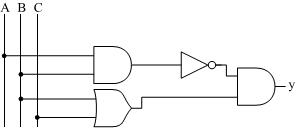

A função lógica realizada por esse circuito combinacional é:

A B C Y

0 0 0 1

0 0 1 1

0 1 0 1

0 1 1 0

1 0 0 0

1 0 1 0

1 1 0 1

1 1 1 0

Assinale a alternativa que apresenta corretamente essa função.

1 - Integradores

2 - Não integradores

( ) Contador

( ) Dupla rampa

( ) Sigma-delta

( ) Aproximações sucessivas

( ) Flash

Assinale a sequência correta.

Considerando que as entradas A, B e C têm como valores possíveis apenas 0 (zero) e 1(um), para que o circuito tenha a sua saída igual a 0 (zero), qual deve ser a configuração das entradas?

Assinale a alternativa que apresenta a expressão lógica equivalente ao circuito.