Questões de Engenharia Eletrônica - Eletrônica Digital na Engenharia Eletrônica para Concurso

Foram encontradas 888 questões

1 - Integradores

2 - Não integradores

( ) Contador

( ) Dupla rampa

( ) Sigma-delta

( ) Aproximações sucessivas

( ) Flash

Assinale a sequência correta.

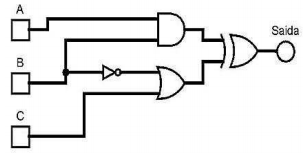

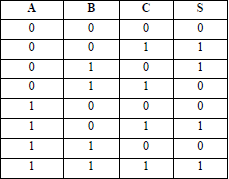

Considerando que as entradas A, B e C têm como valores possíveis apenas 0 (zero) e 1(um), para que o circuito tenha a sua saída igual a 0 (zero), qual deve ser a configuração das entradas?

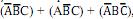

Assinale a alternativa que apresenta a expressão lógica equivalente ao circuito.

De acordo com essas informações, é correto afirmar que a expressão booleana que representa essa lógica é

após simplificada pelo mapa de Karnaugh de três variáveis, é correto afirmar que ela será equivalente à expressão

após simplificada pelo mapa de Karnaugh de três variáveis, é correto afirmar que ela será equivalente à expressão

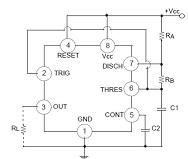

O circuito integrado NE555 é bastante versátil e muito utilizado em circuitos eletrônicos. Considerando que Vcc = 12 v, RA = 1 k Ω, RB=68 kΩ , C1 = 10 uF, C2 = 100 nF, é correto afirmar que a frequência de saída sob a carga RL será de aproximadamente

Caso o referido codificador seja implementado usando apenas lógica combinacional, adotando-se a relação sinal-ruído de quantização como fator de comparação e mantendo-se as mesmas características do sinal de entrada, ele será mais rápido que um conversor A/D equivalente embasado em aproximações sucessivas.

Assumindo que a saída B2 seja o bit mais significativo, um sinal Ve de amplitude 7 V resultará em uma saída representada pelo número 4 no sistema octal.

O mencionado codificador consumirá menos energia se for construído com componentes CMOS que se construído com componentes de lógica TTL.

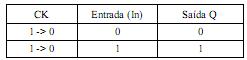

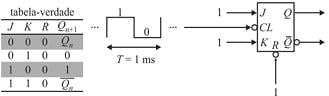

A figura abaixo ilustra um flip-flop JK mestre-escravo, em que J e K são os terminais de entrada; CL é a entrada de clock; R, o terminal de reset; e Q e

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

Na polarização de circuitos integrados lógicos das famílias TTL (transistor-transistor logic) e CMOS (complimentary metal-oxide-semiconductor), são geralmente empregadas fontes de tensão contínua de 10 V.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se, na entrada do conversor A/D, o sinal tiver amplitude de 2 V eficaz e a relação sinal-ruído (SNR) for de 40 dB, então o amplificador terá ganho G igual a 2.000 e a amplitude do ruído será inferior a 10 mV eficaz.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se a tensão de referência do conversor A/D for Vref = 5 V, então a resolução correspondente será inferior a 2 mV.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Para que o conversor A/D não distorça o sinal de entrada, é necessário que a taxa de amostragem mínima seja de 2 × 106 amostras por segundo.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Considere que a resposta em frequência da associação entre buffer e amplificador seja máxima e constante na faixa espectral compreendida entre 1 kHz e 500 MHz. Considere, ainda, que a banda passante dessa associação seja ajustável e possa ser selecionada entre dois valores: 200 MHz e 400 MHz. Nessa situação, a SNR será mínima se o valor de 200 MHz for escolhido para a largura de faixa da associação.

Os circuitos Schmitt-Triggers são utilizados para o acoplamento de dispositivos lentos e dispositivos rápidos. Esses circuitos deixam mais lentas as variações de um sinal rápido, permitindo, assim, o acoplamento de circuitos da família CMOS, mais rápidos, com circuitos da família TTL, geralmente mais lentos

Tanto a família TTL (Transistor-Transistor Logic) como a família ECL (Emitter-Coupled Logic) utilizam transistores bipolares em sua construção; no entanto, a família ECL possui maior velocidade de comutação em comparação com a família TTL.