Questões de Concurso

Sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 894 questões

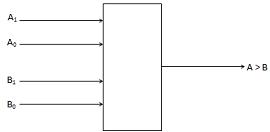

Sabendo que A(A 1A0) e B(B1B0), são palavras binárias de dois bits, a equação lógica que identifica a condição A > B é dada por:

Em um controlador lógico programável (CLP), após definir-se as

variáveis, deve-se desenvolver a lógica de controle para o

funcionamento do dispositivo, podendo essa lógica ser programada

com base nas linguagens definidas de acordo com norma pertinente.

Considerando essas informações e a figura acima, que ilustra um

bloco funcional de um temporizador, julgue os itens a seguir.

Em um controlador lógico programável (CLP), após definir-se as

variáveis, deve-se desenvolver a lógica de controle para o

funcionamento do dispositivo, podendo essa lógica ser programada

com base nas linguagens definidas de acordo com norma pertinente.

Considerando essas informações e a figura acima, que ilustra um

bloco funcional de um temporizador, julgue os itens a seguir.

Em um controlador lógico programável (CLP), após definir-se as

variáveis, deve-se desenvolver a lógica de controle para o

funcionamento do dispositivo, podendo essa lógica ser programada

com base nas linguagens definidas de acordo com norma pertinente.

Considerando essas informações e a figura acima, que ilustra um

bloco funcional de um temporizador, julgue os itens a seguir.

Em um controlador lógico programável (CLP), após definir-se as

variáveis, deve-se desenvolver a lógica de controle para o

funcionamento do dispositivo, podendo essa lógica ser programada

com base nas linguagens definidas de acordo com norma pertinente.

Considerando essas informações e a figura acima, que ilustra um

bloco funcional de um temporizador, julgue os itens a seguir.

Considerando a estrutura do contador acima, julgue os itens que se

seguem, referentes a contadores.

Considerando a estrutura do contador acima, julgue os itens que se

seguem, referentes a contadores.

Considerando a estrutura do contador acima, julgue os itens que se

seguem, referentes a contadores.

os próximos itens.

os próximos itens.

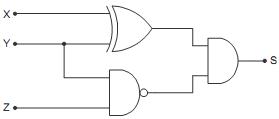

Efetuando-se a minimização do circuito lógico ilustrado acima, obtém-se um circuito equivalente ao de uma porta.

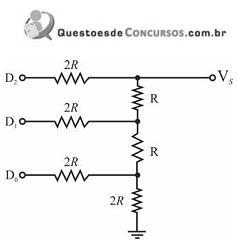

No conversor digital/analógico representado por meio da rede resistiva R-2R acima, cada nível digital Di , i = 0, 1, 2, de entrada, quando ativado no nível lógico 1, equivale a uma tensão CC de 5 volts. No nível lógico 0, essa tensão equivalente é nula. Nesse caso, a entrada digital 010 terá o valor da tensão de saída Vs, em volts, igual a

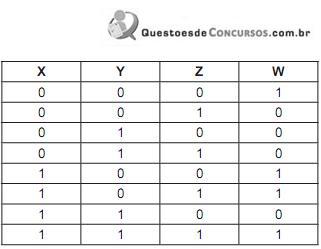

Um circuito digital que realiza tal função lógica é apresentado em

A expressão lógica equivalente de saída é:

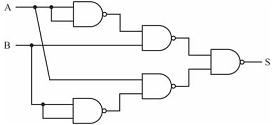

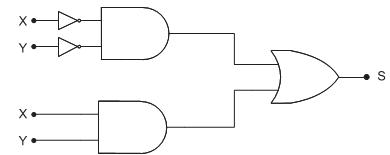

A figura acima mostra um circuito lógico, em que S é a função lógica, e X e Y são variáveis lógicas.

A equação booleana de S, em função de X e Y, é

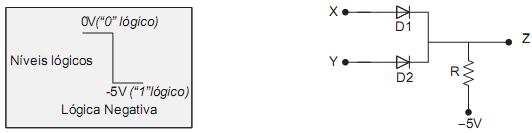

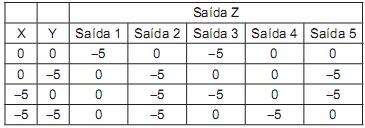

O circuito eletrônico digital acima, composto de diodos ideais, representa uma porta lógica de duas entradas X e Y e uma saída Z. Conforme mostrado na figura, a lógica que é usada é a lógica negativa, na qual o nível de tensão para “0” lógico vale 0V e para “1” lógico vale -5V. A tabela a seguir relaciona os valores das entradas X e Y com possíveis valores de saída.

A saída que corresponde à saída Z do circuito é a

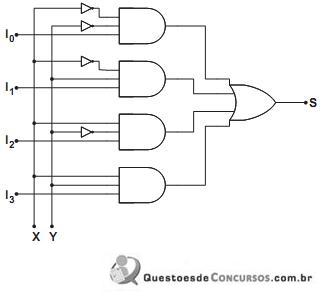

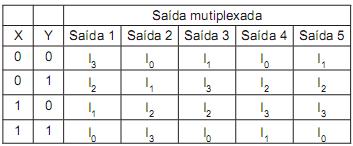

O circuito eletrônico digital da figura é um multiplex com canais de informação I 0 , I 1 , I 2 e I 3 , variáveis de seleção X e Y, e saída multiplexada S.

A seguir, vê-se um quadro com os valores das variáveis X e Y e cinco possíveis saídas.

A representação da Saída Multiplexada S é a saída

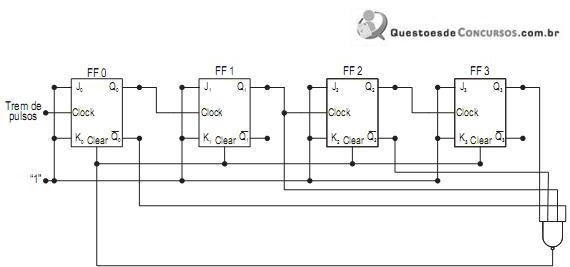

O circuito eletrônico digital acima representa um contador binário e é construído usando-se 4 J-K flip-flops (FF 0,1, 2 e 3), tipo T (entradas J e K ligadas a “1” lógico). Quando a entrada clear recebe um pulso “0”, leva a “0” todas as saídas Q dos flip-flops do circuito. Um trem de pulsos, representado no circuito, excita a entrada Clock do primeiro flip-flop, e, a cada descida do pulso de Clock, o flip-flop muda de estado.

Com base no circuito e nas considerações acima, identifica-se que o circuito representa um contador módulo