Questões de Arquitetura de Computadores - Barramento para Concurso

Foram encontradas 423 questões

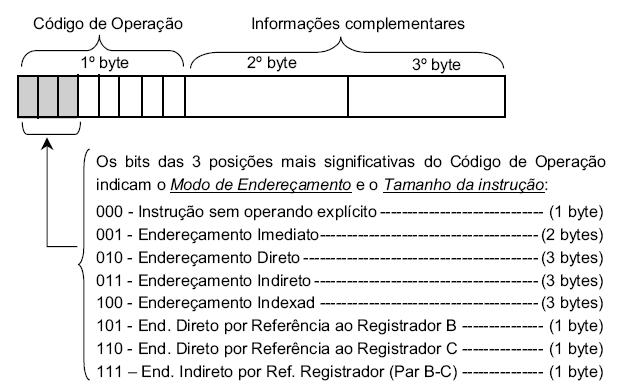

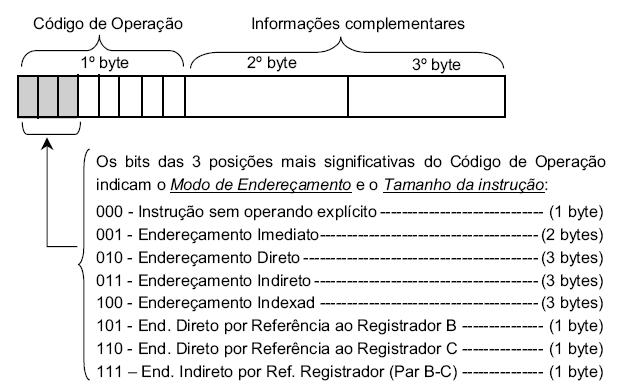

- Todas as instruções usam o Acumulador com 1o operando (implícito) e têm o seguinte significado: "Carregar o Acumulador com o 2o operando, explicitado pelo modo de endereçamento indicado pela instrução".

- Os endereços são armazenados na Memória Principal com sua parte mais significativa na célula de endereço mais alto.

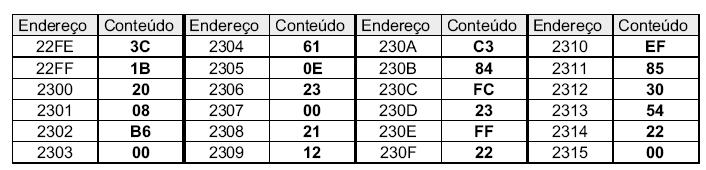

- As memórias locais foram previamentre carregadas com os conteúdos abaixo: Registrador de índice: 02H; Registrador B: 23H; Registrador C: 14H.

Considere o trecho da Memória Principal deste computador, mostrado na tabela abaixo.

Quando o CI=2304, qual será o conteúdo do Acumulador após o processamento da instrução?

I. Não requer, necessariamente, um computador para estabelecer a ligação de dois dispositivos.

II. Com encadeamento de hubs específicos, possibilita a conexão de mais de 100 dispositivos.

III. Utiliza a tecnologia de ligação "hot swapping".

IV. Pode fornecer até 45 watt de potência por porta, permitindo a ligação de dispositivos de consumo moderado sem ligação separada de corrente.

As afirmações acima referem-se, respectivamente, a

I O projeto de um RISC não procura minimizar o tempo gasto nas chamadas a procedimentos, pois programas escritos para esse tipo de processador têm menos chamadas do que os escritos para um CISC.

II Uma técnica para simplificar o conjunto de instruções em um RISC é não prover instruções com modos de endereçamento variados e complexos. Podem também ser reduzidas as instruções que acessam a memória.

III Na arquitetura PC, o front-side-bus (FSB) interliga o processador à memória cache, mas não à memória principal. A freqüência do clock da unidade central de processamento tem que ser a do seu FSB.

IV Os termos IDE, SCSI e SATA designam tipos de interfaces usadas para comunicação com unidades de disco rígido. A SATA é uma interface paralela para comunicação com unidades de disco.

V O projeto de uma memória cache visa aumentar a chance de se encontrar o dado na cache, minimizar o atraso resultante de um dado não estar na cache e minimizar o custo de atualizar a memória principal.

A quantidade de itens certos é igual a