Questões de Concurso Público ABIN 2010 para Oficial Técnico de Inteligência – Área de Engenharia Elétrica

Foram encontradas 148 questões

utilizadas em processos industriais operem com controladores

proporcional-integral-derivativo (PID). Acerca de controlador PID,

julgue os itens a seguir.

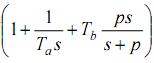

, em que K é o ganho do controlador,

, em que K é o ganho do controlador,  são as constantes de tempo integral e derivativo, respectivamente, e p é um polo para limitação de ganho em altas frequências.

são as constantes de tempo integral e derivativo, respectivamente, e p é um polo para limitação de ganho em altas frequências.

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

estiverem fixadas no nível lógico baixo, é possível que haja dissipação apreciável de potência pelo circuito.

estiverem fixadas no nível lógico baixo, é possível que haja dissipação apreciável de potência pelo circuito.

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

40 MHz seja transmitido por meio de um cabo coaxial a um

conversor analógico/digital (A/D), que realiza conversão com

resoluções de 8 bits e taxa de amostragem

e que se pretenda

e que se pretendaconverter esse sinal analógico em um sinal digital quantizado em 80

níveis diferentes, no mínimo.

Com base nessas informações e considerando, ainda, que

= 1,903 e

= 1,903 e  = 0,3010, julgue os próximos itens.

= 0,3010, julgue os próximos itens.