Questões de Concurso Público Polícia Federal 2014 para Engenheiro Eletricista

Foram encontradas 70 questões

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se a tensão de referência do conversor A/D for Vref = 5 V, então a resolução correspondente será inferior a 2 mV.

O diagrama de blocos acima ilustra o processo de conversão de um sinal analógico em digital. O sinal na entrada tem a forma de onda quadrada com período 1 µs, sem ruído, e amplitude de 1 mV eficaz. O sinal é acoplado ao conversor A/D por meio de um buffer de ganho unitário seguido de um amplificador com ganho G e acoplamento c.a., resultando em ruído branco sobreposto ao sinal. O sinal é então digitalizado por meio de um conversor analógico-digital (A/D) de 12 bits.

Se, na entrada do conversor A/D, o sinal tiver amplitude de 2 V eficaz e a relação sinal-ruído (SNR) for de 40 dB, então o amplificador terá ganho G igual a 2.000 e a amplitude do ruído será inferior a 10 mV eficaz.

Na polarização de circuitos integrados lógicos das famílias TTL (transistor-transistor logic) e CMOS (complimentary metal-oxide-semiconductor), são geralmente empregadas fontes de tensão contínua de 10 V.

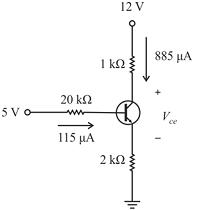

No circuito analógico abaixo, que contém um transistor bipolar de junção do tipo NPN polarizado no modo ativo, a tensão entre coletor e emissor é superior a 8 V e inferior a 10 V.

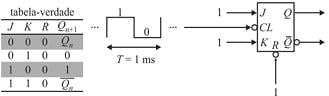

A figura abaixo ilustra um flip-flop JK mestre-escravo, em que J e K são os terminais de entrada; CL é a entrada de clock; R, o terminal de reset; e Q e

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.

são os terminais de saída. O flip-flop obedece à tabela-verdade apresentada, na qual Qn+1e Qn são as saídas após o disparo do clock e antes desse disparo, respectivamente, e o clock é um trem de pulsos com nível adequado de amplitude e período T = 1 ms. Considerando essas informações, é correto afirmar que a saída Q do flip-flop alterna entre os níveis lógicos 1 e 0 a cada 1 ms.