Questões de Concurso Comentadas por alunos sobre eletrônica analógica na engenharia eletrônica em engenharia eletrônica

Foram encontradas 470 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

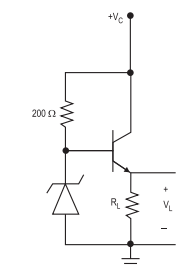

No circuito eletrônico da figura acima, todos os componentes são considerados ideais. O transistor opera com ganho β = 20 e V BE= 0,6 V. Sabe-se que o diodo Zener opera com tensão nominal de 6 V, que o circuito deve funcionar com a tensão VC podendo assumir valores entre 15 e 30 V e que a resistência de carga RL é incerta, podendo variar de 5 Ω até infinito (circuito sem carga). O projeto prevê que a tensão V L , com alguma tolerância, permaneça constante. Nesse contexto, o diodo Zener deverá ser especificado no projeto para suportar uma potência máxima, em W, de

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.