Questões de Concurso Comentadas por alunos sobre eletrônica digital na engenharia eletrônica em engenharia eletrônica

Foram encontradas 520 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

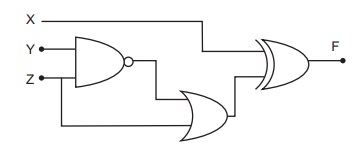

O circuito lógico combinacional mostrado na figura acima tem, como entradas, as variáveis lógicas X, Y e Z e, como saída, a variável F. A expressão simplificada da função booleana F é

O circuito acima representa uma porta lógica digital

implementada com a tecnologia NMOS. Os transistores de

chaveamento (com entradas

) são idênticos e do tipo

) são idênticos e do tipoenriquecimento, mas o transistor de carga é do tipo depleção. As

tensões de limiar dos transistores de chaveamento e carga são 1 V

e !3 V, respectivamente. Para esse circuito, o nível lógico alto (1

digital) é definido como qualquer tensão analógica compreendida

entre 3,5 V e 5 V, e o nível lógico baixo (0 digital) corresponde às

tensões analógicas entre 0 e 1,8 V. Esse circuito apresenta duas

peculiaridades:

I se pelo menos um dos transistores de chaveamento operar com

entrada em 5 V, a tensão de saída

não excederá 0,3 V;

não excederá 0,3 V;II somente com ambas as entradas simultaneamente no nível

lógico baixo, a saída atinge o nível lógico alto.

Com base nessas informações, julgue os itens subsequentes.

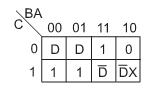

Desconsiderando-se os inversores, a menor soma de produtos que implementa o mapa acima possui

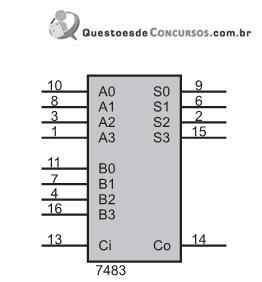

Deseja-se projetar um circuito, usando-se apenas um somador de 4 bits tipo 7483, que converta um número D4D3D2D1D0 , em representação BCD de 5 bits (0 a 19), para um número B4B3B2B1B0 em representação binária de 5 bits. Para isso, basta zerar Ci e tomar as saídas do somador, desde que as entradas A3A2A1A0 e B3B2B1B0 sejam, respectivamente,