Questões de Concurso

Foram encontradas 225 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Uma arquitetura de computador hipotética utiliza um microprocessador que possui instruções com o modo de endereçamento “endereçamento indireto por registrador”. Considere a instrução de máquina a seguir, que utiliza esse tipo de endereçamento, envolvendo o registrador R1.

ADD A,(R1), 8

Considerando esse contexto, e que A representa o acumulador, 8 representa um valor imediato e ADD é o mnemônico de uma instrução de máquina que realiza a operação soma, assinale a alternativa que apresenta uma funcionalidade coerente para essa instrução e que utiliza o endereçamento indireto por registrador.

Analise as alternativas:

I. RDM–Registrador de Dados da Memória, armazena temporariamente o endereço de acesso a uma posição de memória, ao se iniciar a operação de leitura ou escrita.

II. Os registradores são memórias estáticas (SRAM).

III. REM–Registrador de Endereços da Memória, armazena temporariamente a informação que está sendo transferida da MP para a UCP (leitura) ou da UCP para MP (escrita).

IV. As memórias estáticas (SRAM) são bem mais rápidas.

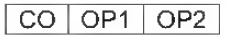

Um determinado computador possui uma arquitetura na qual o contador de instruções (Cl) possui 16 bits; o registrador de instruções (RI) possui 40 bits e as instruções possuem o modelo

no qual, CO é o código de operação, OP1 é o

operando 1 e OP2 é o operando 2, sendo que OP1 e

OP2 possuem, cada um, 16 bits. Nessa arquitetura, o

CO tem o tamanho (em bits) igual a: