Questões de Concurso Para itaipu binacional

Foram encontradas 3.211 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

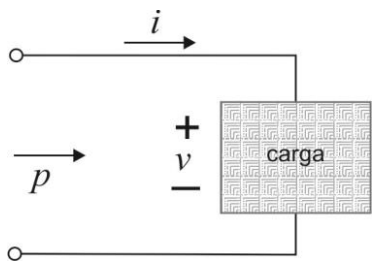

A potência fornecida a uma carga, em um circuito como o ilustrado na figura ao lado, é definida por p = vi. Considere, para fins de avaliação, que a carga ilustrada está conectada na rede e identifique como verdadeiras (V) ou falsas (F) as seguintes afirmativas:

( ) A corrente (i) é uma grandeza senoidal e pode ser descrita como Im*sen(ωt+ θ).

( ) A tensão (v) é uma grandeza senoidal e pode ser descrita como Vm*sen(ωt).

( ) Nos circuitos indutivos, θ é positivo (v adiantada em relação a i).

( ) Nos circuitos capacitivos, θ é negativo (i adiantada em relação a v).

Assinale a alternativa que apresenta a sequência correta, de cima para baixo.

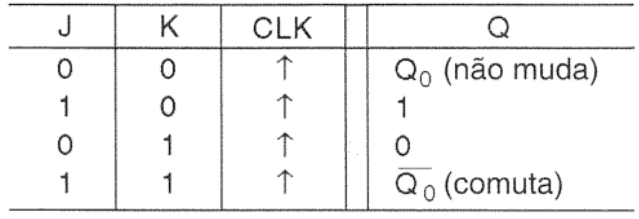

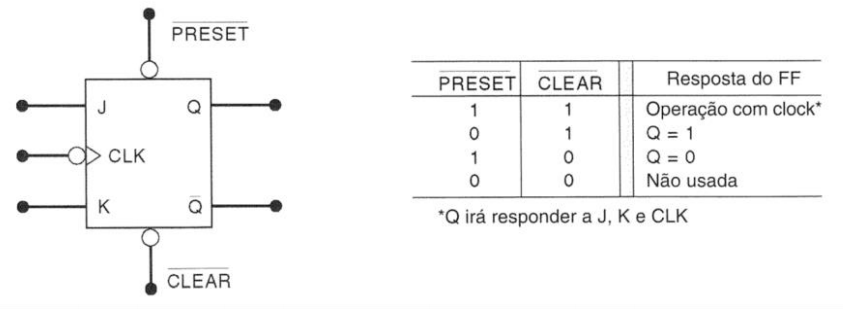

Flip-flop é um circuito digital pulsado (uso de clock) utilizado como uma memória de um bit. Com relação ao assunto, identifique como verdadeiras (V) ou falsas (F) as seguintes afirmativas:

( ) A tabela verdade de um flip-flop J-K com clock é a seguinte:

( ) O flip-flop disparado por transição faz uso de um detector de transição para garantir que a saída vai responder à entrada somente quando uma transição de disparo do sinal de clock ocorrer. Caso esse detector não seja utilizado, o circuito resultante vai operar como um latch do tipo C.

( ) A tabela verdade de um flip-flop assíncrono JCLK é a apresentada abaixo:

( ) Os atrasos de propagação ocorrem sempre que um sinal causa a mudança de estado da saída de um flip-flop.

Assinale a alternativa que apresenta a sequência correta, de cima para baixo

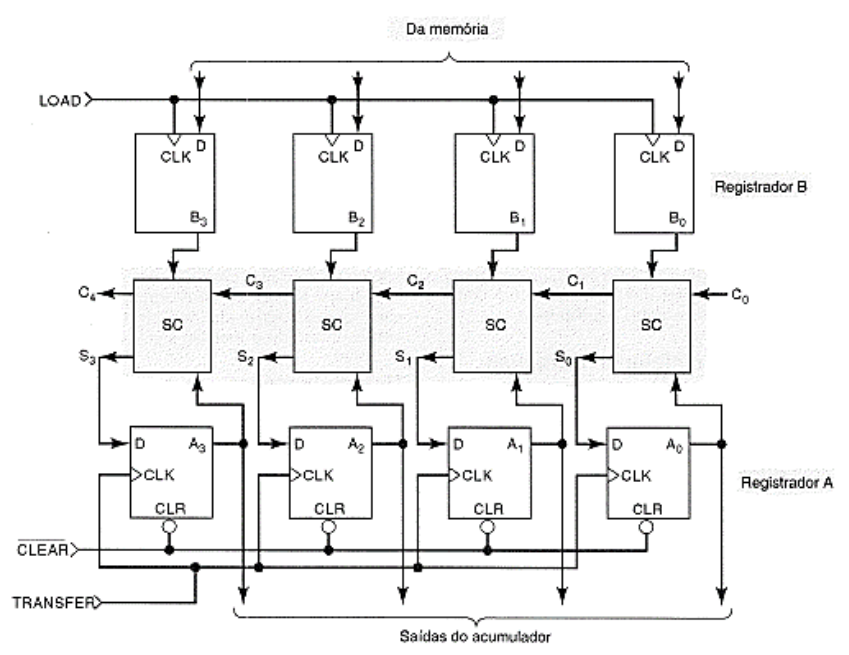

Considere o esquemático de circuito abaixo:

Esse esquemático representa:

Um algoritmo avalia valores obtidos de dois sistemas de aquisição, o SISTEMA A e o SISTEMA B. O SISTEMA A comunica-se com valores na base hexadecimal, e o SISTEMA B, na base octal. Os valores são capturados e multiplicados um pelo outro, na forma r = SISTEMA A*SISTEMA B, e o resultado da operação é nominado de r. O valor de r é então convertido em binário e armazenado em uma variável de 16 bits, aqui nominada de s. No caso da ocorrência de overflow (valor r >= 216), todos os 16 bits são marcados com 1, indicando uma leitura não válida. Acerca disso, considere as seguintes entradas:

• SISTEMA A = 1AD16 e SISTEMA B = 58 • SISTEMA A = 1F716 e SISTEMA B = 128 • SISTEMA A = AA116 e SISTEMA B = 148

Essas entradas geram, respectivamente, as seguintes sequências de s: