Questões de Concurso

Para cti

Foram encontradas 680 questões

Resolva questões gratuitamente!

Junte-se a mais de 4 milhões de concurseiros!

Considerando as tecnologias de empacotamento de circuito integrado (CI), julgue o item a seguir.

A tecnologia de interconexões wire-bonding é apropriada

para uso em alta densidade de conexões, com mais de 200

I/Os por chip.

Considerando as tecnologias de empacotamento de circuito integrado (CI), julgue o item a seguir.

A tecnologia de empilhamento 3D de chips utilizando vias

de silício oferece a possibilidade de solucionar problemas de

interconexão, ao mesmo tempo em que possibilita o uso de

funções integradas para melhoria de desempenho.

No projeto de um sistema VLSI em modo misto utilizando VHDL padrão, pode-se empregar a mesma metodologia de simulação para os componentes digitais e analógicos, uma vez que a linguagem oferece suporte uniforme para a simulação de ambos os tipos de circuitos sem necessidade de adaptações específicas para cada domínio.

Na implementação de um PLL (phase-locked loop) em modo misto usando Verilog HDL, é aconselhável utilizar o mesmo conjunto de primitivas e elementos de modelagem empregados para blocos digitais, como flip-flops e lógica combinacional, para garantir a coerência na representação do comportamento do sistema de controle de fase e frequência.

Na verificação física de sistemas VLSI em modo misto, a integridade do sinal e as considerações de ruído são menos críticas para circuitos analógicos que para circuitos digitais, tornando o roteamento e a disposição dos componentes analógicos menos importantes no processo de design.

As linguagens HDL, como VHDL e Verilog, em conjunto com extensões associadas podem ser úteis para a simulação de sistemas VLSI em modo misto, pois permitem a modelagem com precisão adequada tanto de componentes digitais quanto analógicos, facilitando a análise e verificação do design antes da fabricação física.

As abordagens de design para circuitos analógicos diferem significativamente das utilizadas em circuitos digitais, principalmente no que diz respeito à gestão de ruídos e variações de sinal; além disso, a integração de componentes analógicos em designs de modo misto requer considerações adicionais para assegurar a compatibilidade e o desempenho efetivo do circuito integrado como um todo.

Para otimizar a eficiência dos circuitos analógicos e de modo misto, uma prática comum é utilizar trilhas estreitas de polissilício para rotas de sinais que carregam corrente, visando reduzir a capacitância parasita, mesmo que isso possa resultar em um aumento da resistência do circuito; essa abordagem é frequentemente empregada na indústria para melhorar o desempenho geral do circuito.

Nos circuitos integrados VLSI de modo misto que priorizam a eficiência energética e a minimização de consumo, a concepção de amplificadores diferenciais é invariavelmente orientada pelo uso exclusivo de transistores PMOS.

Em sistemas CMOS VLSI, a integração de materiais piezoelétricos com avanços em nanotecnologia é realizada geralmente por meio de abordagens híbridas, em que os componentes são fabricados separadamente e depois combinados com o chip CMOS; isso assegura a eficiência e funcionalidade do conjunto, contribuindo significativamente para a sustentabilidade e autonomia energética desses dispositivos, sem comprometer as características individuais de cada tecnologia.

A tecnologia de semicondutor de óxido metálico complementar destaca-se no cenário de implementação de sinais mistos em tecnologia VLSI por sua capacidade de otimizar a densidade e a eficiência energética na esfera digital, bem como à sua versatilidade em fornecer um leque diversificado e adequado de componentes para a elaboração de projetos no espectro analógico.

Em projetos de sistemas VLSI de modo misto, a utilização de áreas de guarda (guard rings) e a separação física dos blocos analógicos e digitais visam minimizar a interferência indesejada, garantindo a integridade do sinal analógico e o desempenho adequado do sistema como um todo.

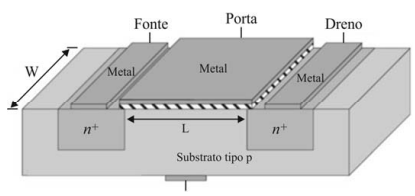

Considerando a figura precedente, que ilustra a geometria de uma porta do tipo MOS, julgue o item a seguir.

A resistência elétrica da camada dielétrica de óxido sob a

porta metálica do MOSFET é inferior à resistência do canal

semicondutor quando polarizado.

Considerando a figura precedente, que ilustra a geometria de uma porta do tipo MOS, julgue o item a seguir.

Nas regiões de dreno e fonte do MOSFET ilustrado, a

dopagem é superior àquela aplicada ao substrato tipo p.

Considerando a figura precedente, que ilustra a geometria de uma porta do tipo MOS, julgue o item a seguir.

A ilustração mostra a estrutura de um transistor PMOS do

tipo depleção.

Considerando a figura precedente, que ilustra a geometria de uma porta do tipo MOS, julgue o item a seguir.

Na ilustração, a dimensão identificada por W corresponde à

largura do canal do MOSFET.

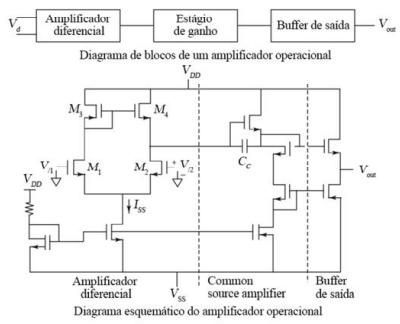

No processo de design de um amplificador operacional CMOS, a seleção do tamanho dos dispositivos MOSFET e das correntes de polarização tem influência direta em parâmetros tais como ganho, CMRR, dissipação de potência, ruído e taxa de variação (slew rate). Esse processo é iterativo e requer ajustes baseados em simulações, em que aumentar o tamanho dos MOSFETs (aumentando W) com uma menor VGS (tensão entre porta e fonte) pode melhorar o emparelhamento, aumentar o ganho e reduzir o ruído, porém, podendo resultar em uma área de layout maior e potencialmente em menor velocidade de operação.

No amplificador operacional CMOS mostrado, o amplificador diferencial deve fornecer a maior parte do ganho do sistema, enquanto o estágio de ganho em fonte comum serve principalmente para prover a compensação de frequência necessária; o buffer de saída é utilizado para equalizar as tensões de entrada diferencial sem amplificar o sinal.

Em relação a circuitos integrados em larga escala de fabricação (VLSI), julgue o item que se segue.

Nos circuitos CMOS, devido à diferença de mobilidade entre

lacunas e elétrons em materiais semicondutores, os

transistores NMOS usados em circuitos digitais têm

aproximadamente o dobro do tamanho dos transistores

PMOS.

Em relação a circuitos integrados em larga escala de fabricação (VLSI), julgue o item que se segue.

Em materiais semicondutores fabricados com silício, a

mobilidade de elétrons é maior que a mobilidade das

lacunas, por isso, na fabricação de circuitos de alto

desempenho e baixo consumo, é empregada,

predominantemente, a tecnologia que utiliza apenas

transistores NMOS.