Questões de Concurso Militar EEAR 2009 para Sargento da Aeronáutica - Eletrônica (Turma 2)

Foram encontradas 55 questões

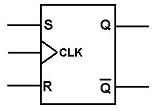

No flip flop abaixo, a entrada clock (CLK) é ativada por

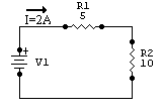

Qual é a potência dissipada por R2, em Watts, no circuito abaixo?

Obs.: os valores dos resistores estão em Ωs.

Assinale a alternativa que completa corretamente as lacunas da assertiva abaixo.

“Um __________________ opera com _________ entradas para gerar uma soma e um carry como saídas.”

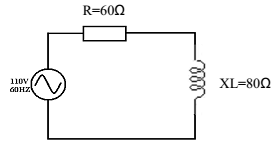

Qual o valor, em Ohms, da impedância total do circuito abaixo?

Coloque (V) para verdadeiro e (F) para falso para as afirmações abaixo, e marque a alternativa com a sequência correta.

( ) Um circuito está em ressonância quando a reatância indutiva XL é igual à reatância capacitiva XC.

( ) Num circuito LC real em paralelo, a impedância ZT é máxima na frequência de ressonância.

( ) Um circuito RLC em série, operando numa freqüência abaixo da freqüência de ressonância, possui uma XC menor que XL.

Assinale a alternativa que completa, correta e respectivamente, as lacunas do texto abaixo.

“A análise CA de um circuito que utiliza dispositivos FET requer o desenvolvimento de um modelo CA de pequeno sinal para o dispositivo. Um dos principais componentes do modelo CA reflete o fato de que uma ___________ aplicada aos terminais porta-fonte do dispositivo controla a __________ entre os terminais dreno-fonte.

Assinale a alternativa que completa, correta e respectivamente, as lacunas da frase abaixo.

Um amplificador operando em classe _______ possui um ciclo de operação _______.

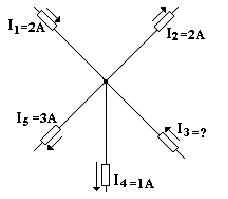

Analise a figura a seguir e calcule o valor de I3.

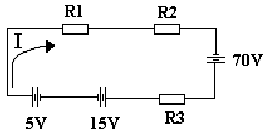

Analise a figura abaixo e calcule a corrente I, em Amperes, e as quedas de tensão, em Volts, através de R1, R2, e R3.

Dados:

R1=15Ω

R2=5 Ω

R3=10 Ω

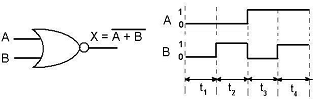

Quais são os níveis lógicos na saída da porta abaixo, nos tempos t1 e t4 , respectivamente?

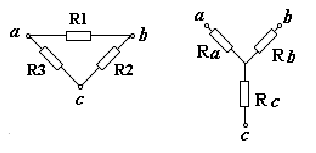

Transforme a rede ∆ (delta) abc na sua rede Υ equivalente.

Dados:

R1=3Ω

R2=5 Ω

R3=2 Ω

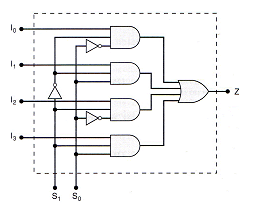

A figura abaixo representa um

Em se tratando de famílias lógicas e circuitos integrados (CI), coloque (V) para verdadeiro e (F) para falso e, a seguir, assinale a alternativa que apresenta a sequência correta.

( ) A presença de um chanfro, num dos lados de um encapsulamento DIP (dual in line package), tem por finalidade possibilitar a localização do pino 1 do CI.

( ) O termo fan-out (também denominado fator de acionamento de carga) é definido como o número máximo de entradas lógicas que a saída de um circuito lógico pode acionar com segurança.

( ) Para as especificações da série TTL padrão, a tensão de entrada deve ser menor do que 0,8V ou maior do que 2,0V. Uma tensão de entrada entre 0,8 e 2,0V é considerada inválida e produzirá uma resposta de saída imprevisível, portanto tem de ser evitada.