Questões de Concurso

Sobre álgebra booleana e circuitos lógicos em engenharia eletrônica em engenharia eletrônica

Foram encontradas 505 questões

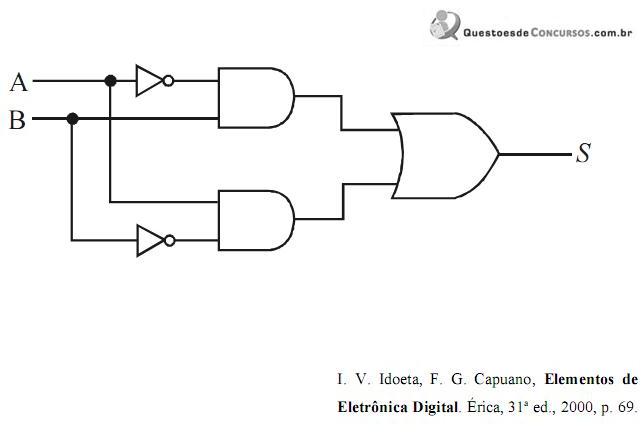

Tendo como base o circuito lógico mostrado na figura acima, e

considerando os sinais aplicados às entradas A e B, julgue os

itens que se seguem.

A respeito do circuito lógico acima, julgue o item a seguir.

A respeito do circuito lógico acima, julgue o item a seguir.A expressão booleana resultante para a saída S é S=A.B.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Considerando a tabela-verdade acima, que descreve o

comportamento de um circuito convencional com três

entradas e uma saída, e na qual X representa dont’care

(não importa), julgue os itens seguintes.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

do flip-flop do tipo D sempre estará em nível lógico alto.

do flip-flop do tipo D sempre estará em nível lógico alto.

Um encoder incremental possui dois sinais de saída, na forma de onda

quadrada, de mesma freqüência e defasados em ¼ de ciclo. Assumindo que

as saídas dos canais tenham ciclo de trabalho de 50%, existem duas

possibilidades para a temporização dos mesmos, conforme indicado por caso

A e caso B na figura acima. Os sinais do encoder incremental são

processados pelo circuito digital indicado na mesma figura. Acerca do

funcionamento desse circuito em regime permanente, e considerando que

todos os componentes do circuito são ideais, julgue os itens subseqüentes.

estivesse sempre em nível alto, a porta ou-exclusivo (exclusive-Or) inverteria o sinal

estivesse sempre em nível alto, a porta ou-exclusivo (exclusive-Or) inverteria o sinal

a seguir.

a seguir.

Considere o trecho de programa da família 8051.

MOV A,#3FH

INC A

MOV P1,A

Ao final, o port P1, em binário, terá

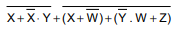

A expressão lógica  está

simplificada em

está

simplificada em

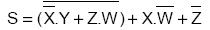

pode ser simplificada como

pode ser simplificada como

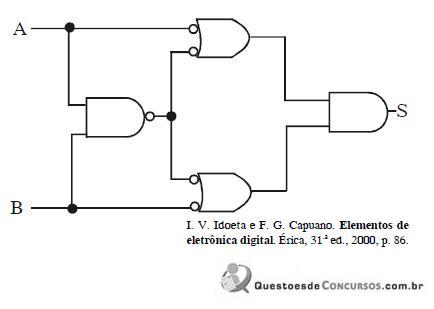

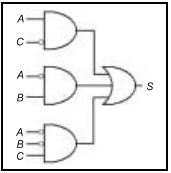

A figura acima mostra o diagrama esquemático de um circuito combinacional com entradas A, B e C e uma saída S. Considerando que o circuito seja implementado com lógica TTL, julgue os itens a seguir.

Se a entrada C estiver flutuando, ou seja, não houver tensão conectada a essa entrada, a saída S assumirá o valor lógico 0 independentemente do valor das outras entradas.